# GigaDevice Semiconductor Inc.

# GD32VF103 RISC-V 32-bit MCU

# **User Manual**

Revision 1.3

(Jun. 2021)

# **Table of Contents**

| Table of       | f Contents                                  | 2          |

|----------------|---------------------------------------------|------------|

| List of F      | Figures                                     | 14         |

| List of 1      | Tables                                      | 20         |

|                | tem and memory architecture                 |            |

|                | RISC-V CPU                                  |            |

|                |                                             |            |

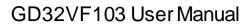

|                | System architecture                         |            |

| 1.3.           | Memory map                                  |            |

| 1.3.1          | ,                                           |            |

| 1.3.2          | 2. On-chip flash memory overview            | 28         |

| 1.4.           | Boot configuration                          | 28         |

| 1.5.           | Device electronic signature                 | <b>2</b> 9 |

| 1.5.1          | 1. Memory density information               | 30         |

| 1.5.2          |                                             |            |

| 2. Flas        | sh memory controller (FMC)                  | 32         |

|                | Overview                                    |            |

|                |                                             |            |

|                | Characteristics                             |            |

| 2.3.           | Function overview                           | 32         |

| 2.3.1          |                                             |            |

| 2.3.2          |                                             |            |

| 2.3.3          | _                                           |            |

| 2.3.4          | 3                                           |            |

| 2.3.5          |                                             |            |

| 2.3.6          | 1 0 0                                       |            |

| 2.3.7<br>2.3.8 | •                                           |            |

| 2.3.0          |                                             |            |

| 2.3.1          |                                             |            |

| 2.3.1          |                                             |            |

| 2.4.           | Register definition                         |            |

| 2.4.1          |                                             |            |

| 2.4.2          |                                             |            |

| 2.4.3          |                                             |            |

| 2.4.4          |                                             |            |

| 2.4.5          |                                             |            |

| 2.4.6          | · ,                                         |            |

| 2.4.7          | 7. Option byte status register (FMC_OBSTAT) | 44         |

|    | 2.4.                | .8. | Erase/Program Protection register (FMC_WP)     |    |

|----|---------------------|-----|------------------------------------------------|----|

|    | 2.4.                | .9. | Product ID register (FMC_PID)                  | 45 |

| 3. | Po                  | wer | management unit (PMU)                          | 46 |

|    | 3.1.                | Ove | erview                                         | 46 |

|    | 3.2.                | Cha | aracteristics                                  | 46 |

|    | 3.3.                | Fur | nction overview                                | 46 |

|    | 3.3.                | .1. | Battery backup domain                          | 47 |

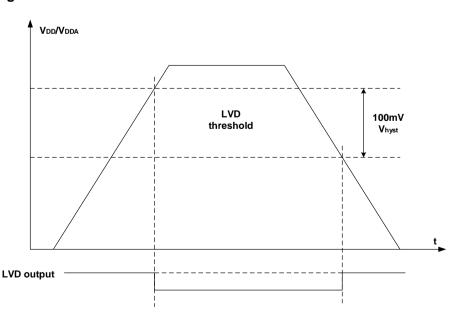

|    | 3.3.                | .2. | V <sub>DD</sub> /V <sub>DDA</sub> power domain | 48 |

|    | 3.3.                | .3. | 1.2V power domain                              | 50 |

|    | 3.3.                | .4. | Power saving modes                             | 50 |

|    | 3.4.                | Reg | gister definition                              | 53 |

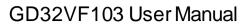

|    | 3.4.                | .1. | Control register (PMU_CTL)                     | 53 |

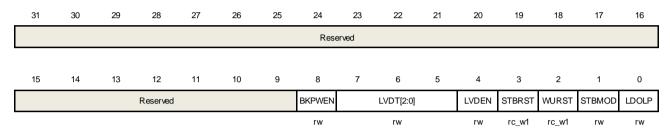

|    | 3.4.                | .2. | Control and status register (PMU_CS)           | 54 |

| 4. | Ba                  | cku | p registers (BKP)                              | 56 |

|    | 4.1.                | Ove | erview                                         | 56 |

|    | 4.2.                | Cha | aracteristics                                  | 56 |

|    | 4.3.                |     | nction overview                                |    |

|    | <b>4.3.</b><br>4.3. |     | RTC clock calibration                          |    |

|    | 4.3.<br>4.3.        |     | Tamper detection                               |    |

|    |                     |     | ·                                              |    |

|    | 4.4.                | •   | gister definition                              |    |

|    | 4.4.<br>4.4.        |     | Backup data register x (BKP_DATAx) (x= 041)    |    |

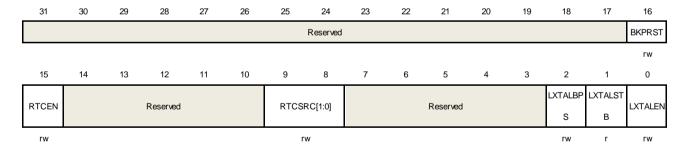

|    |                     |     | RTC signal output control register (BKP_OCTL)  |    |

|    | 4.4.                |     | Tamper pin control register (BKP_TPCTL)        |    |

| _  | 4.4.                |     | Tamper control and status register (BKP_TPCS)  |    |

| 5. |                     |     | and clock unit (RCU)                           | 61 |

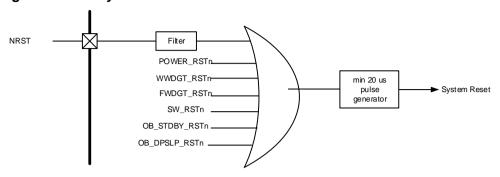

|    | 5.1.                |     | set control unit (RCTL)                        |    |

|    | 5.1.                |     | Overview                                       |    |

|    | 5.1.                |     | Function overview                              |    |

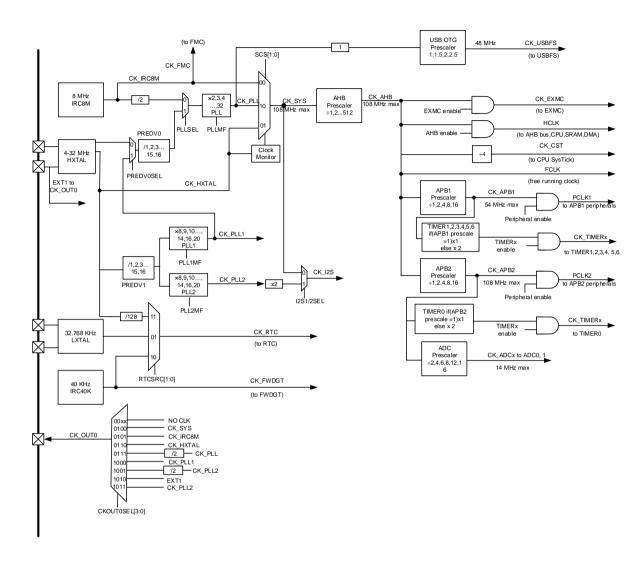

|    | 5.2.                |     | ck control unit (CCTL)                         |    |

|    | 5.2.                |     | Overview                                       |    |

|    | 5.2.                |     | Characteristics                                |    |

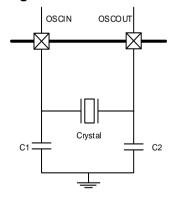

|    | 5.2.                |     | Function overview                              |    |

|    | 5.3.                |     | gister definition                              |    |

|    | 5.3.                |     | Control register (RCU_CTL)                     |    |

|    | 5.3.                |     | Clock configuration register 0 (RCU_CFG0)      |    |

|    | 5.3.                |     | Clock interrupt register (RCU_INT)             |    |

|    | 5.3.                |     | APB2 reset register (RCU_APB2RST)              |    |

|    | 5.3.                |     | APB1 reset register (RCU_APB1RST)              |    |

|    | 5.3.                | .b. | AHB enable register (RCU_AHBEN)                | 80 |

|    | 5.3.                                                               | 7.                                                                                                    | APB2 enable register (RCU_APB2EN)                                                                                                                                                                                                                                                                                                                 | 82                          |

|----|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

|    | 5.3.8                                                              | 8.                                                                                                    | APB1 enable register (RCU_APB1EN)                                                                                                                                                                                                                                                                                                                 | 83                          |

|    | 5.3.9                                                              | 9.                                                                                                    | Backup domain control register (RCU_BDCTL)                                                                                                                                                                                                                                                                                                        | 86                          |

|    | 5.3.                                                               | 10.                                                                                                   | Reset source/clock register (RCU_RSTSCK)                                                                                                                                                                                                                                                                                                          | 87                          |

|    | 5.3.                                                               | 11.                                                                                                   | AHB reset register (RCU_AHBRST)                                                                                                                                                                                                                                                                                                                   | 89                          |

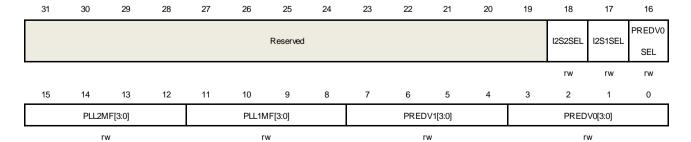

|    | 5.3.                                                               | 12.                                                                                                   | Clock configuration register 1 (RCU_CFG1)                                                                                                                                                                                                                                                                                                         | 89                          |

|    | 5.3.                                                               | 13.                                                                                                   | Deep-sleep mode voltage register (RCU_DSV)                                                                                                                                                                                                                                                                                                        | 92                          |

| 3. | Inte                                                               | erru                                                                                                  | pt/event controller (EXTI)                                                                                                                                                                                                                                                                                                                        | 93                          |

| (  | 6.1.                                                               | Ove                                                                                                   | erview                                                                                                                                                                                                                                                                                                                                            | 93                          |

| (  | 6.2.                                                               | Cha                                                                                                   | racteristics                                                                                                                                                                                                                                                                                                                                      | 93                          |

| (  | 6.3.                                                               | Fun                                                                                                   | ction overview                                                                                                                                                                                                                                                                                                                                    | 93                          |

| (  | 6.4.                                                               | Ext                                                                                                   | ernal interrupt and event (EXTI) block diagram                                                                                                                                                                                                                                                                                                    | 96                          |

| (  | 6.5.                                                               | Ext                                                                                                   | ernal Interrupt and Event function overview                                                                                                                                                                                                                                                                                                       | 96                          |

| (  | 6.6.                                                               | Reg                                                                                                   | ister definition                                                                                                                                                                                                                                                                                                                                  | 98                          |

|    | 6.6.                                                               | 1.                                                                                                    | Interrupt enable register (EXTI_INTEN)                                                                                                                                                                                                                                                                                                            | 98                          |

|    | 6.6.2                                                              | 2.                                                                                                    | Event enable register (EXTI_EVEN)                                                                                                                                                                                                                                                                                                                 | 98                          |

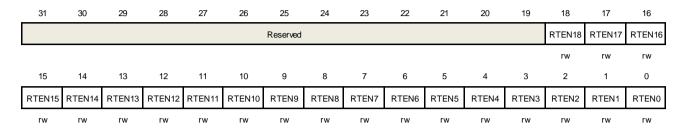

|    | 6.6.3                                                              | 3.                                                                                                    | Rising edge trigger enable register (EXTI_RTEN)                                                                                                                                                                                                                                                                                                   | 99                          |

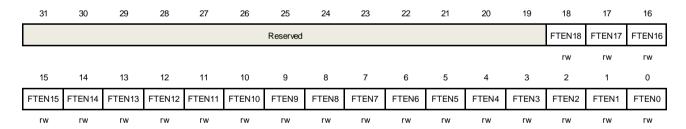

|    | 6.6.4                                                              | 4.                                                                                                    | Falling edge trigger enable register (EXTI_FTEN)                                                                                                                                                                                                                                                                                                  | 99                          |

|    | 6.6.                                                               | 5.                                                                                                    | Software interrupt event register (EXTI_SWIEV)                                                                                                                                                                                                                                                                                                    | 99                          |

|    | 6.6.                                                               | 6.                                                                                                    | Pending register (EXTI_PD)                                                                                                                                                                                                                                                                                                                        | 100                         |

|    |                                                                    |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                   |                             |

| 7. | Gei                                                                | nera                                                                                                  | al-purpose and alternate-function I/Os (GPIO and AFIO)                                                                                                                                                                                                                                                                                            | 101                         |

|    | Gei<br>7.1.                                                        |                                                                                                       | al-purpose and alternate-function I/Os (GPIO and AFIO)                                                                                                                                                                                                                                                                                            |                             |

| -  |                                                                    | Ove                                                                                                   |                                                                                                                                                                                                                                                                                                                                                   | 101                         |

|    | 7.1.                                                               | Ove<br>Cha                                                                                            | erview                                                                                                                                                                                                                                                                                                                                            | 101                         |

|    | 7.1.<br>7.2.<br>7.3.                                               | Ove<br>Cha<br>Fun                                                                                     | racteristics                                                                                                                                                                                                                                                                                                                                      | 101                         |

|    | 7.1.<br>7.2.<br>7.3.                                               | Ove<br>Cha<br>Fun<br>1.                                                                               | racteristics                                                                                                                                                                                                                                                                                                                                      | 101101101102                |

|    | <b>7.1. 7.2. 7.3.</b> 7.3.                                         | Ove<br>Cha<br>Fun<br>1.                                                                               | ction overview.  GPIO pin configuration                                                                                                                                                                                                                                                                                                           | 101101101102103             |

|    | <b>7.1. 7.2. 7.3.</b> 7.3. 7.3.                                    | Ove<br>Cha<br>Fun<br>1.<br>2.                                                                         | ction overview.  GPIO pin configuration  External interrupt/event lines                                                                                                                                                                                                                                                                           | 101101102103                |

|    | <b>7.1. 7.2. 7.3.</b> 7.3. 7.3. 7.3.                               | Ove<br>Cha<br>Fun<br>1.<br>2.<br>3.<br>4.                                                             | ction overview                                                                                                                                                                                                                                                                                                                                    | 101101102103103             |

|    | <b>7.1. 7.2. 7.3.</b> 7.3.2 7.3.3 7.3.3 7.3.4                      | Ove<br>Cha<br>Fun<br>1.<br>2.<br>3.<br>4.                                                             | ction overview.  GPIO pin configuration                                                                                                                                                                                                                                                                                                           | 101101102103103103          |

|    | <b>7.1. 7.2. 7.3. 7.3. 7.3. 7.3. 7.3. 7.3. 7.3.</b>                | Ove<br>Cha<br>Fun<br>1.<br>2.<br>3.<br>4.<br>5.                                                       | ction overview                                                                                                                                                                                                                                                                                                                                    | 101101102103103103104       |

|    | <b>7.1. 7.2. 7.3.</b> 7.3. 7.3. 7.3. 7.3. 7.3. 7.3. 7.3.           | Ove<br>Cha<br>Fun<br>1.<br>2.<br>3.<br>4.<br>5.<br>6.                                                 | ction overview.  GPIO pin configuration  External interrupt/event lines  Alternate functions (AF)  Input configuration  Output configuration  Analog configuration                                                                                                                                                                                | 101101102103103104104104    |

|    | <b>7.1. 7.2. 7.3. 7.3. 7.3. 7.3. 7.3. 7.3. 7.3. 7.3. 7.3. 7.3.</b> | Ove<br>Cha<br>Fun<br>1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>7.                                           | ction overview                                                                                                                                                                                                                                                                                                                                    | 101101102103103104104105    |

|    | 7.1. 7.2. 7.3. 7.3. 7.3. 7.3. 7.3. 7.3. 7.3                        | Cha<br>Fun<br>1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>7.<br>8.<br>9.                                      | ction overview                                                                                                                                                                                                                                                                                                                                    | 101101101102                |

|    | <b>7.1. 7.2. 7.3.</b> 7.3. 7.3. 7.3. 7.3. 7.3. 7.3. 7.3.           | Ove<br>Cha<br>Fun<br>1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>7.<br>8.<br>9.<br>Ren                        | ction overview  GPIO pin configuration  External interrupt/event lines  Alternate functions (AF)  Input configuration  Output configuration  Analog configuration  Alternate function (AF) configuration  IO pin function selection  GPIO locking function  napping function I/O and debug configuration  Introduction                            | 101101102103103104105105106 |

|    | <b>7.1. 7.2. 7.3.</b> 7.3. 7.3. 7.3. 7.3. 7.3. 7.3. 7.3.           | Cha<br>Fun<br>1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>7.<br>8.<br>9.<br>Ren<br>1.                         | ction overview.  GPIO pin configuration  External interrupt/event lines.  Alternate functions (AF).  Input configuration.  Output configuration.  Analog configuration.  Alternate function (AF) configuration.  IO pin function selection.  GPIO locking function.  mapping function I/O and debug configuration.  Introduction.  Main features. | 101101102                   |

|    | <b>7.1. 7.2. 7.3.</b> 7.3. 7.3. 7.3. 7.3. 7.3. 7.3. 7.3.           | Ove<br>Cha<br>Fun<br>1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>7.<br>8.<br>9.<br>Ren<br>1.<br>2.            | ction overview                                                                                                                                                                                                                                                                                                                                    | 101101102                   |

|    | <b>7.1. 7.2. 7.3.</b> 7.3. 7.3. 7.3. 7.3. 7.3. 7.3. 7.3.           | Ove<br>Cha<br>1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>7.<br>8.<br>9.<br>Ren<br>1.<br>2.<br>3.             | croin overview                                                                                                                                                                                                                                                                                                                                    | 101101101102                |

|    | <b>7.1. 7.2. 7.3.</b> 7.3. 7.3. 7.3. 7.3. 7.3. 7.3. 7.3.           | Ove<br>Cha<br>1.<br>2.<br>3.<br>4.<br>5.<br>6.<br>7.<br>8.<br>9.<br>Ren<br>1.<br>2.<br>3.<br>4.<br>5. | ction overview                                                                                                                                                                                                                                                                                                                                    | 101101102                   |

|    | 7.4.7.  | SPI0 AF remapping                                   | 109 |

|----|---------|-----------------------------------------------------|-----|

|    | 7.4.8.  | SPI2/I2S2 AF remapping                              | 109 |

|    | 7.4.9.  | CAN0 AF remapping                                   | 109 |

|    | 7.4.10  | . CAN1 AF remapping                                 | 110 |

|    | 7.4.11  | . CLK pins AF remapping                             | 110 |

|    | 7.5. R  | egister definition                                  | 111 |

|    | 7.5.1.  | Port control register 0 (GPIOx_CTL0, x=AE)          | 111 |

|    | 7.5.2.  | Port control register 1 (GPIOx_CTL1, x=AE)          | 113 |

|    | 7.5.3.  | Port input status register (GPIOx_ISTAT, x=AE)      | 114 |

|    | 7.5.4.  | Port output control register (GPIOx_OCTL, x=AE)     | 115 |

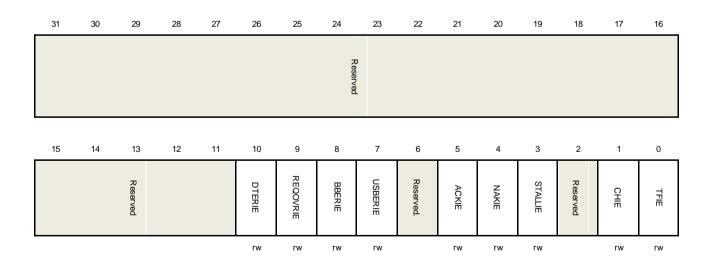

|    | 7.5.5.  | Port bit operate register (GPIOx_BOP, x=AE)         | 115 |

|    | 7.5.6.  | Port bit clear register (GPIOx_BC, x=AE)            | 116 |

|    | 7.5.7.  | Port configuration lock register (GPIOx_LOCK, x=AE) | 116 |

|    | 7.5.8.  | Event control register (AFIO_EC)                    |     |

|    | 7.5.9.  | AFIO port configuration register 0 (AFIO_PCF0)      | 118 |

|    | 7.5.10  | . EXTI sources selection register 0 (AFIO_EXTISS0)  | 121 |

|    | 7.5.11  | . EXTI sources selection register 1 (AFIO_EXTISS1)  | 122 |

|    | 7.5.12  | EXTI sources selection register 2 (AFIO_EXTISS2)    | 123 |

|    | 7.5.13  | EXTI sources selection register 3 (AFIO_EXTISS3)    | 124 |

|    | 7.5.14  | AFIO port configuration register 1 (AFIO_PCF1)      | 125 |

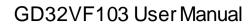

| 8. | CRC     | calculation unit (CRC)                              | 127 |

|    |         | verview                                             |     |

|    |         |                                                     |     |

|    | 8.2. C  | haracteristics                                      | 127 |

|    | 8.3. F  | unction overview                                    | 128 |

|    | 8.4. R  | egister definition                                  | 129 |

|    | 8.4.1.  |                                                     |     |

|    | 8.4.2.  |                                                     |     |

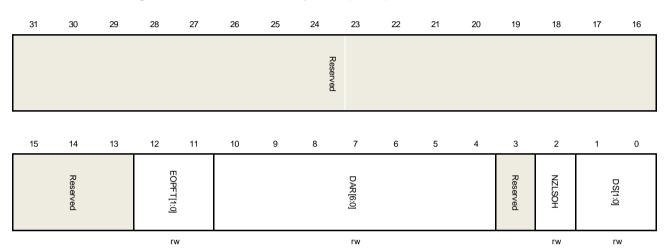

|    | 8.4.3.  | Control register (CRC_CTL)                          | 130 |

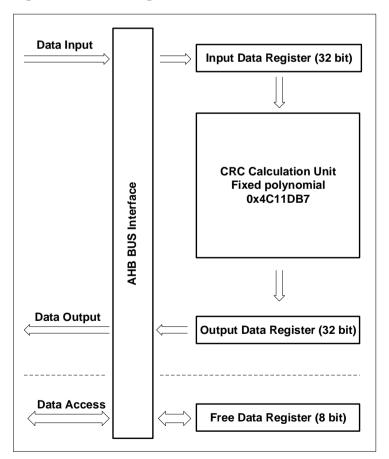

| 9. | Direc   | et memory access controller (DMA)                   |     |

|    |         |                                                     |     |

|    | 9.1. O  | verview                                             | 131 |

|    | 9.2. C  | haracteristics                                      | 131 |

|    | 9.3. B  | lock diagram                                        | 132 |

|    | 9.4. Fi | unction overview                                    | 132 |

|    | 9.4.1.  | DMA operation                                       |     |

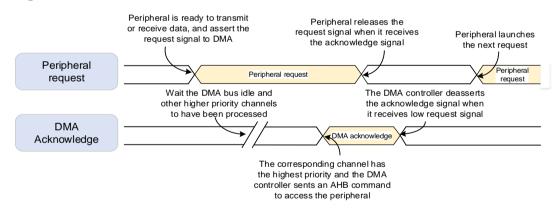

|    | 9.4.2.  | Peripheral handshake                                |     |

|    | 9.4.3.  | Arbitration                                         |     |

|    | 9.4.4.  | Address generation                                  |     |

|    | 9.4.5.  | Circular mode                                       |     |

|    | 9.4.6.  | Memory to memory mode                               |     |

|    | JJ.     |                                                     |     |

|    | 9.4.7.  | Channel configuration                               | 135 |

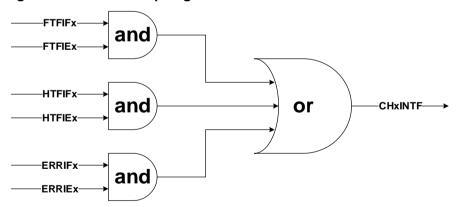

| 9.4.8.  | Interrupt                                                                 | 136   |

|---------|---------------------------------------------------------------------------|-------|

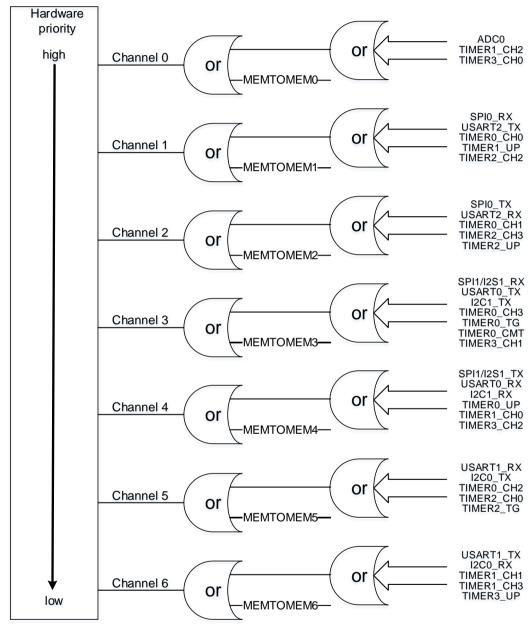

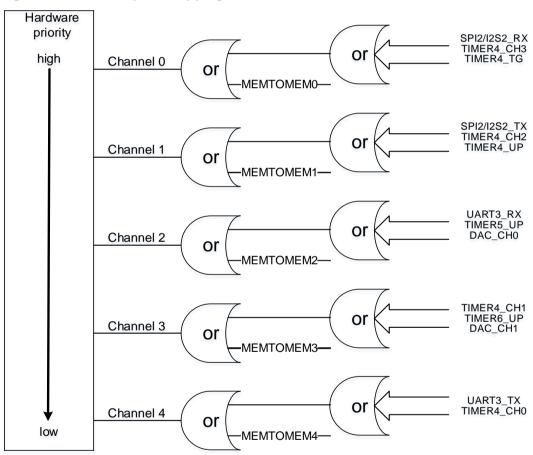

| 9.4.9.  | DMA request mapping                                                       | 136   |

| 9.5. R  | egister definition                                                        | 140   |

| 9.5.1.  | Interrupt flag register (DMA_INTF)                                        | 140   |

| 9.5.2.  | Interrupt flag clear register (DMA_INTC)                                  | 141   |

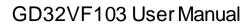

| 9.5.3.  | Channel x control register (DMA_CHxCTL)                                   | 141   |

| 9.5.4.  | Channel x counter register (DMA_CHxCNT)                                   | 143   |

| 9.5.5.  | Channel x peripheral base address register (DMA_CHxPADDR)                 | 144   |

| 9.5.6.  | Channel x memory base address register (DMA_CHxMADDR)                     | 144   |

| 10. Del | oug (DBG)                                                                 | 146   |

| 10.1.   | Overview                                                                  | 146   |

| 10.2.   | JTAG function overview                                                    | 146   |

| 10.2.1  | Pin assignment                                                            | 146   |

| 10.2.2  | JTAG daisy chained structure                                              | 146   |

| 10.2.3  | Debug reset                                                               | 147   |

| 10.3.   | Debug hold function overview                                              | 147   |

| 10.3.1  | Debug support for power saving mode                                       | 147   |

| 10.3.2  |                                                                           |       |

| 10.4.   | Register definition                                                       | 148   |

| 10.4.1  | . ID code register (DBG_ID)                                               | 148   |

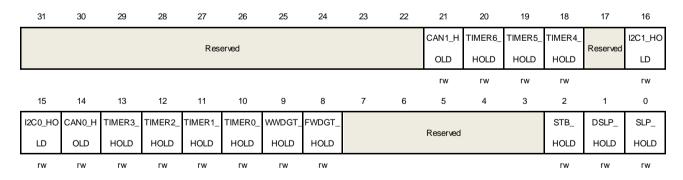

| 10.4.2  |                                                                           |       |

| 11. Ana | nlog-to-digital converter (ADC)                                           | 151   |

| 11.1.   | Introduction                                                              | 151   |

| 11.2.   | Main features                                                             | 151   |

| 11.3.   | Pins and internal signals                                                 | 152   |

| 11.4.   | Functional description                                                    | 152   |

| 11.4.1  | •                                                                         |       |

| 11.4.2  | ,                                                                         |       |

| 11.4.3  |                                                                           |       |

| 11.4.4  |                                                                           |       |

| 11.4.5  | Conversion modes                                                          | 154   |

| 11.4.6  |                                                                           |       |

| 11.4.7  |                                                                           |       |

| 11.4.8  | Programmable sample time                                                  | 160   |

| 11.4.9  | External trigger                                                          | 160   |

| 11.4.10 | D. DMA request                                                            | 161   |

| 11.4.1  | 1. Temperature sensor, and internal reference voltage V <sub>REFINT</sub> | 161   |

| 11.4.1  | 2. Programmable resolution (DRES) - fast conversion mode                  | 162   |

| 11.4.1  | 3. On-chip hardware oversampling                                          | 162   |

| 44 -    | ADC arms made                                                             | 4.6.4 |

| 11.6.   | Free mode                                                     | 165 |

|---------|---------------------------------------------------------------|-----|

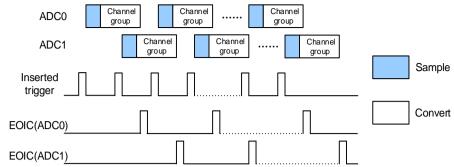

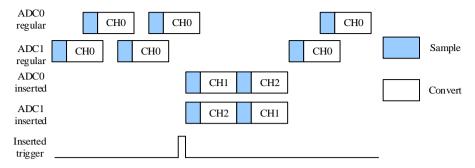

| 11.6.1  | . Regular parallel mode                                       | 166 |

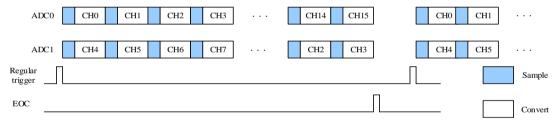

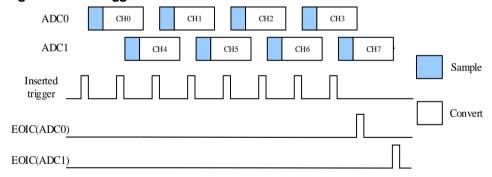

| 11.6.2  | 2. Inserted parallel mode                                     | 166 |

| 11.6.3  | 3. Follow-up fast mode                                        | 167 |

| 11.6.4  | Follow-up slow mode                                           | 167 |

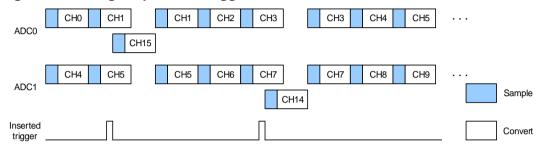

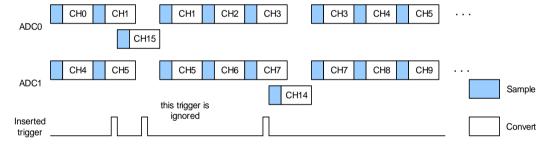

| 11.6.5  | i. Trigger rotation mode                                      | 168 |

| 11.6.6  | Combined regular parallel & inserted parallel mode            | 169 |

| 11.6.7  | Combined regular parallel & trigger rotation mode             | 169 |

| 11.6.8  | Combined inserted parallel & follow-up mode                   | 170 |

| 11.7.   | ADC interrupts                                                | 171 |

| 11.8.   | ADC registers                                                 | 172 |

| 11.8.1  | . Status register (ADC_STAT)                                  | 172 |

| 11.8.2  | Control register 0 (ADC_CTL0)                                 | 173 |

| 11.8.3  | 8. Control register 1 (ADC_CTL1)                              | 175 |

| 11.8.4  | Sample time register 0 (ADC_SAMPT0)                           | 177 |

| 11.8.5  | i. Sample time register 1 (ADC_SAMPT1)                        | 178 |

| 11.8.6  | 6. Inserted channel data offset register x (ADC_IOFFx) (x=03) | 179 |

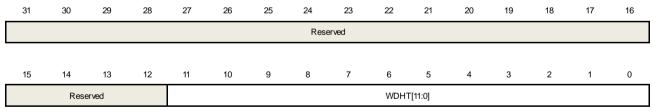

| 11.8.7  | . Watchdog high threshold register (ADC_WDHT)                 | 179 |

| 11.8.8  | 8. Watchdog low threshold register (ADC_WDLT)                 | 180 |

| 11.8.9  | ). Regular sequence register 0 (ADC_RSQ0)                     | 180 |

| 11.8.1  | 0. Regular sequence register 1 (ADC_RSQ1)                     | 181 |

| 11.8.1  | Regular sequence register 2 (ADC_RSQ2)                        | 181 |

| 11.8.1  | 2. Inserted sequence register (ADC_ISQ)                       | 182 |

| 11.8.1  | 3. Inserted data register x (ADC_IDATAx) (x= 03)              | 182 |

| 11.8.1  | 4. Regular data register (ADC_RDATA)                          | 183 |

| 11.8.1  | 5. Oversample control register (ADC_OVSAMPCTL)                | 183 |

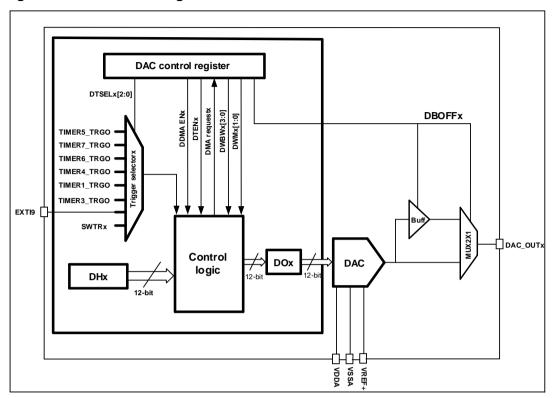

| 12. Dig | gital-to-analog converter (DAC)                               | 186 |

| 12.1.   | Overview                                                      | 186 |

| 12.2.   | Characteristics                                               | 186 |

| 12.3.   | Function overview                                             | 187 |

| 12.3.1  | DAC enable                                                    | 187 |

| 12.3.2  | 2. DAC output buffer                                          | 187 |

| 12.3.3  | B. DAC data configuration                                     | 188 |

| 12.3.4  | I. DAC trigger                                                | 188 |

| 12.3.5  | 5. DAC conversion                                             | 188 |

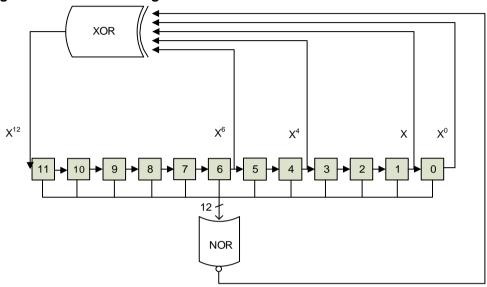

| 12.3.6  |                                                               |     |

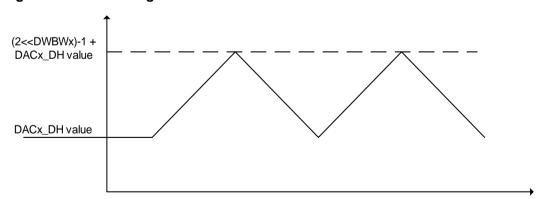

| 12.3.7  | 1 5                                                           |     |

| 12.3.8  | 3. DMA request                                                | 190 |

| 12.3.9  | DAC concurrent conversion                                     | 190 |

| 12.4.   | Register definition                                           | 191 |

| 12.4.1  | 0 ( = /                                                       |     |

| 12.4.2  | 2. Software trigger register (DAC_SWT)                        | 193 |

| 12.4.3.      | DAC0 12-bit right-aligned data holding register (DAC0_R12DH)                 | 194 |

|--------------|------------------------------------------------------------------------------|-----|

| 12.4.4.      | DAC0 12-bit left-aligned data holding register (DAC0_L12DH)                  | 194 |

| 12.4.5.      | DAC0 8-bit right-aligned data holding register (DAC0_R8DH)                   | 195 |

| 12.4.6.      | DAC1 12-bit right-aligned data holding register (DAC1_R12DH)                 | 195 |

| 12.4.7.      | DAC1 12-bit left-aligned data holding register (DAC1_L12DH)                  | 196 |

| 12.4.8.      | DAC1 8-bit right-aligned data holding register (DAC1_R8DH)                   | 196 |

| 12.4.9.      | DAC concurrent mode 12-bit right-aligned data holding register (DACC_R12DH)  | 196 |

| 12.4.10      | . DAC concurrent mode 12-bit left-aligned data holding register (DACC_L12DH) | 197 |

| 12.4.11      | . DAC concurrent mode 8-bit right-aligned data holding register (DACC_R8DH)  | 198 |

| 12.4.12      | . DAC0 data output register (DAC0_DO)                                        | 198 |

| 12.4.13      | . DAC1 data output register (DAC1_DO)                                        | 199 |

| 13. Wate     | chdog timer (WDGT)                                                           | 200 |

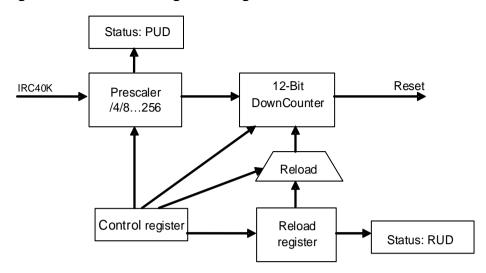

| <b>13.1.</b> | Free watchdog timer (FWDGT)                                                  | 200 |

| 13.1.1.      | Overview                                                                     |     |

| 13.1.2.      | Characteristics                                                              | 200 |

| 13.1.3.      | Function overview                                                            |     |

| 13.1.4.      | Register definition                                                          |     |

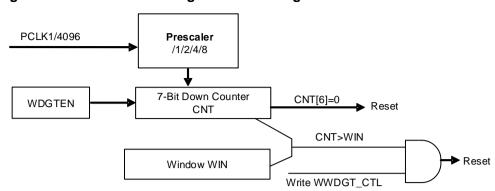

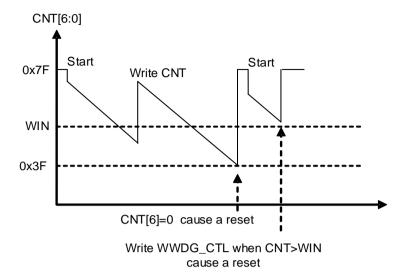

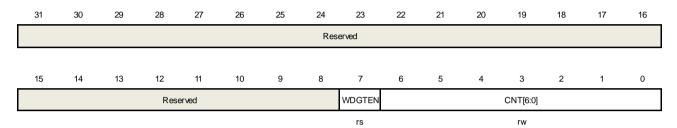

|              | Window watchdog timer (WWDGT)                                                |     |

| 13.2.1.      | Overview                                                                     |     |

| 13.2.2.      | Characteristics                                                              |     |

| 13.2.3.      | Function overview                                                            |     |

| 13.2.4.      | Register definition                                                          |     |

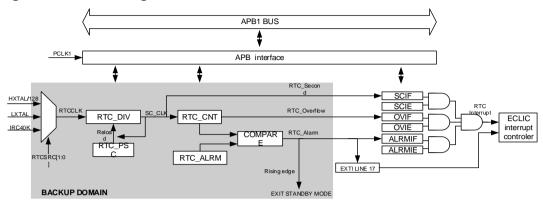

| 14. Rea      | l-time Clock (RTC)                                                           | 211 |

| 14.1.        | Overview                                                                     | 211 |

| 14.2.        | Characteristics                                                              | 211 |

| <b>14.3.</b> | Function overview                                                            | 211 |

| 14.3.1.      | RTC reset                                                                    | 212 |

| 14.3.2.      | RTC reading                                                                  | 212 |

| 14.3.3.      | RTC configuration                                                            | 212 |

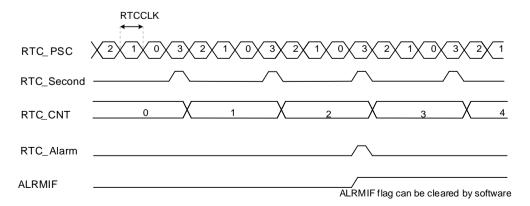

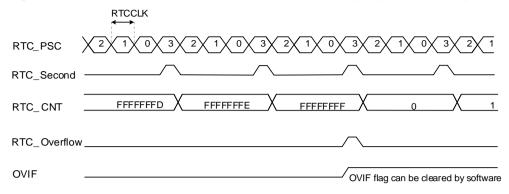

| 14.3.4.      | RTC flag assertion                                                           | 213 |

| <b>14.4.</b> | Register definition                                                          | 215 |

| 14.4.1.      | RTC interrupt enable register(RTC_INTEN)                                     | 215 |

| 14.4.2.      | RTC control register(RTC_CTL)                                                | 215 |

| 14.4.3.      | RTC prescaler high register (RTC_PSCH)                                       | 216 |

| 14.4.4.      | RTC prescaler low register (RTC_PSCL)                                        | 217 |

| 14.4.5.      | RTC divider high register (RTC_DIVH)                                         | 217 |

| 14.4.6.      | RTC divider low register (RTC_DIVL)                                          | 217 |

| 14.4.7.      | RTC counter high register (RTC_CNTH)                                         | 218 |

| 14.4.8.      | RTC counter low register (RTC_CNTL)                                          | 218 |

| 14.4.9.      | RTC alarm high register (RTC_ALRMH)                                          | 219 |

| 14.4 10      | RTC alarm low register (RTC_ALRML)                                           | 219 |

| 15. Tim | er(TIMERx)                                                    | 220 |

|---------|---------------------------------------------------------------|-----|

| 15.1.   | Advanced timer (TIMERx, x=0)                                  | 220 |

| 15.1.1  | Overview                                                      | 220 |

| 15.1.2  | Characteristics                                               | 221 |

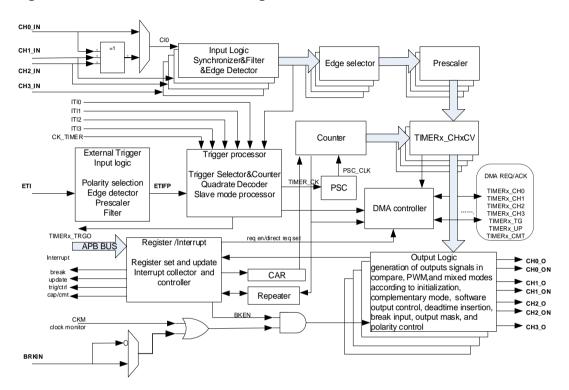

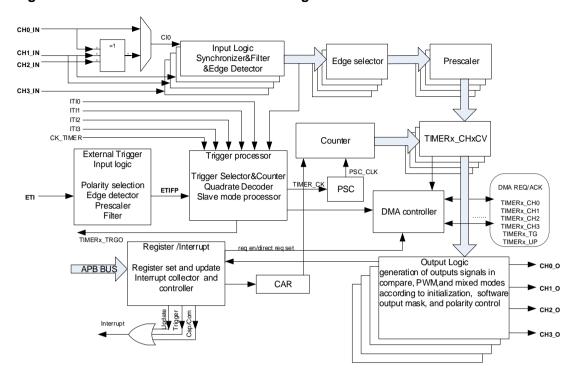

| 15.1.3  | Block diagram                                                 | 222 |

| 15.1.4  | Function overview                                             | 222 |

| 15.1.5  | TIMERx registers(x=0)                                         | 252 |

| 15.2.   | General level0 timer (TIMERx, x=1, 2, 3, 4)                   | 277 |

| 15.2.1  | Overview                                                      | 277 |

| 15.2.2  |                                                               |     |

| 15.2.3  | <b>5</b>                                                      |     |

| 15.2.4  | Function overview                                             | 278 |

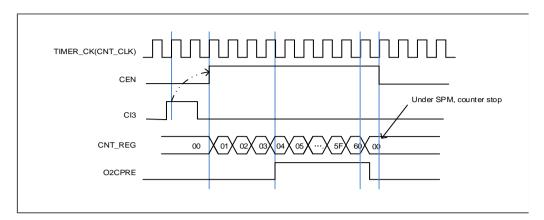

| 15.2.5  | TIMERx registers(x=1,2,3,4)                                   | 294 |

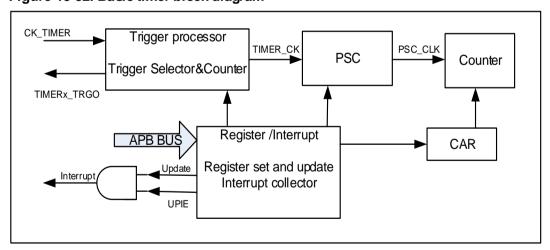

| 15.3.   | Basic timer (TIMERx, x=5, 6)                                  | 315 |

| 15.3.1  |                                                               |     |

| 15.3.2  |                                                               |     |

| 15.3.3  | 5                                                             |     |

| 15.3.4  |                                                               |     |

| 15.3.5  | TIMERx registers(x=5,6)                                       | 320 |

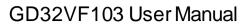

| 16. Uni | versal synchronous/asynchronous receiver /transmitter (USART) | 325 |

| 16.1.   | Overview                                                      | 325 |

| 16.2.   | Characteristics                                               | 325 |

| 16.3.   | Function overview                                             | 326 |

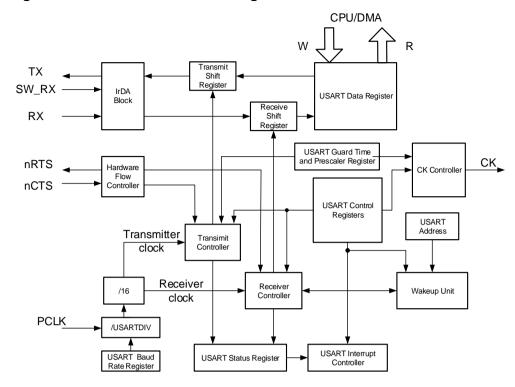

| 16.3.1  | USART frame format                                            | 327 |

| 16.3.2  | Baud rate generation                                          | 328 |

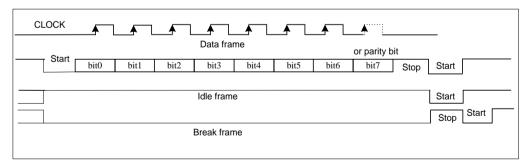

| 16.3.3  | USART transmitter                                             | 328 |

| 16.3.4  | USART receiver                                                | 329 |

| 16.3.5  | Use DMA for data buffer access                                | 331 |

| 16.3.6  | Hardware flow control                                         | 332 |

| 16.3.7  | Multi-processor communication                                 | 333 |

| 16.3.8  | LIN mode                                                      | 334 |

| 16.3.9  | Synchronous mode                                              | 335 |

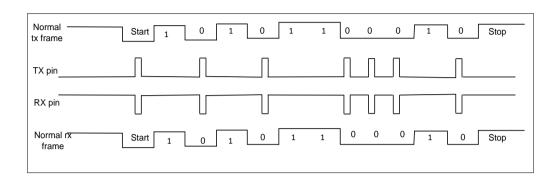

| 16.3.1  | ). IrDA SIR ENDEC mode                                        | 336 |

| 16.3.1  | I. Half-duplex communication mode                             | 337 |

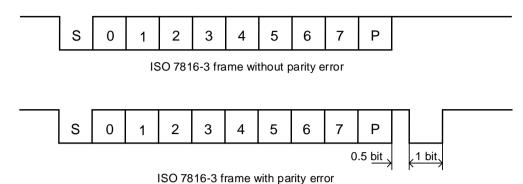

| 16.3.1  | 2. Smartcard (ISO7816-3) mode                                 | 337 |

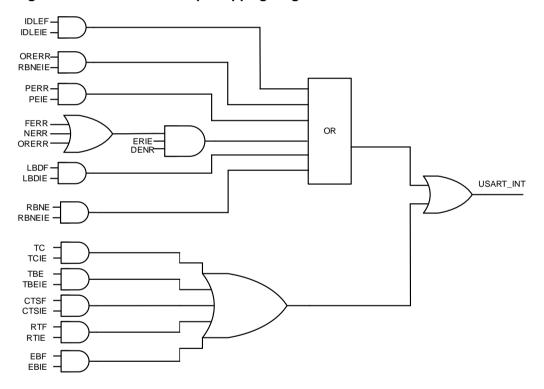

| 16.3.1  | 3. USART interrupts                                           | 338 |

| 16.4.   | Register definition                                           | 340 |

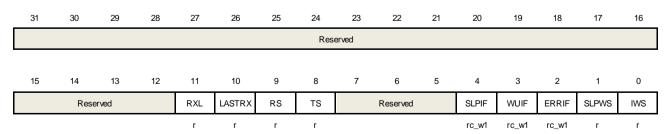

| 16.4.1  | Status register (USART_STAT)                                  | 340 |

| 16.4.2  | Data register (USART_DATA)                                    | 342 |

| 16.4.3  | Baud rate register (USART_BAUD)                               | 342 |

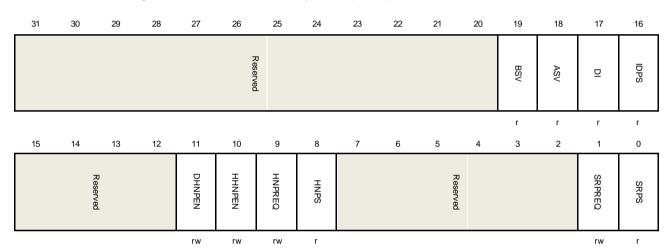

| 16.4.4  | Control register 0 (USART CTL0)                               | 343 |

| 16   | 3.4.5.      | Control register 1 (USART_CTL1)                  | 345 |

|------|-------------|--------------------------------------------------|-----|

| 16   | 6.4.6.      | Control register 2 (USART_CTL2)                  | 346 |

| 16   | 6.4.7.      | Guard time and prescaler register (USART_GP)     | 348 |

| 17.  | Inter       | -integrated circuit interface (I2C)              | 350 |

| 17.1 | l. <b>(</b> | Overview                                         | 350 |

| 17.2 | 2. (        | Characteristics                                  | 350 |

| 17.3 | 3. F        | unction overview                                 | 350 |

| 17   | 7.3.1.      | SDA and SCL lines                                | 351 |

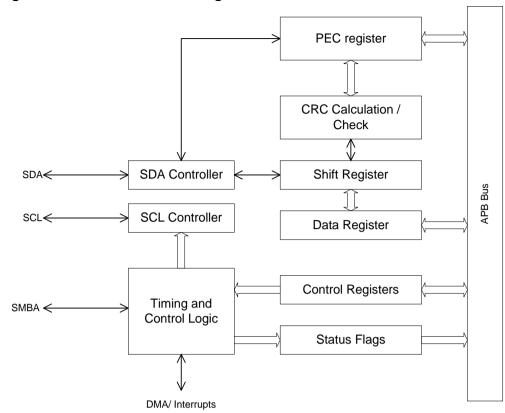

| 17   | 7.3.2.      | Data validation                                  | 352 |

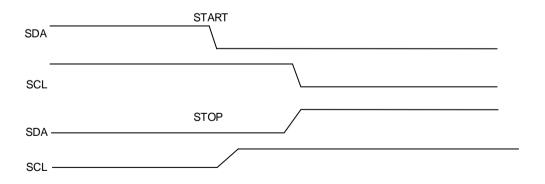

| 17   | 7.3.3.      | START and STOP condition                         | 352 |

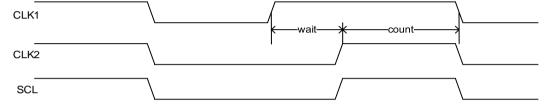

| 17   | 7.3.4.      | Clock synchronization                            | 352 |

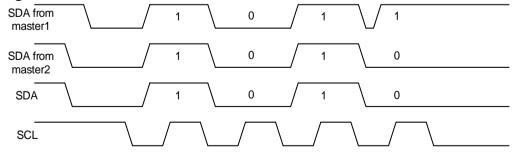

| 17   | 7.3.5.      | Arbitration                                      | 353 |

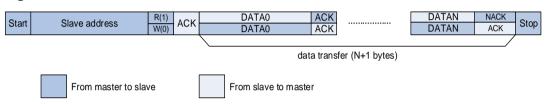

| 17   | 7.3.6.      | I2C communication flow                           | 353 |

| 17   | 7.3.7.      | Programming model                                | 354 |

| 17   | 7.3.8.      | SCL line stretching                              |     |

|      | 7.3.9.      | Use DMA for data transfer                        |     |

|      | 7.3.10.     | 3                                                |     |

|      | 7.3.11.     | • •                                              |     |

| 17   | 7.3.12.     | '                                                |     |

| 17.4 | l. F        | Register definition                              | 367 |

| 17   | 7.4.1.      | Control register 0 (I2C_CTL0)                    | 367 |

| 17   | 7.4.2.      | Control register 1 (I2C_CTL1)                    |     |

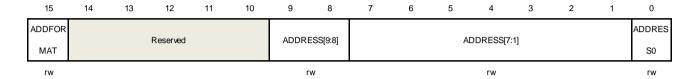

| 17   | 7.4.3.      | Slave address register 0 (I2C_SADDR0)            |     |

|      | 7.4.4.      | Slave address register 1 (I2C_SADDR1)            |     |

|      | 7.4.5.      | Transfer buffer register (I2C_DATA)              |     |

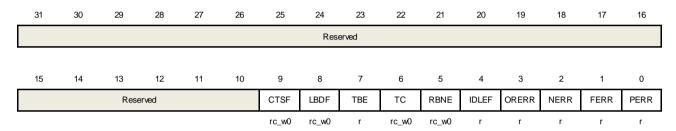

|      | 7.4.6.      | Transfer status register 0 (I2C_STAT0)           |     |

|      | 7.4.7.      | Transfer status register 1 (I2C_STAT1)           |     |

|      | 7.4.8.      | Clock configure register (I2C_CKCFG)             |     |

|      | 7.4.9.      | Rise time register (I2C_RT)                      |     |

|      | 7.4.10.     | 3. 1. 3. 1. ( = 1. 1)                            |     |

| 18.  |             | al peripheral interface/Inter-IC sound (SPI/I2S) |     |

| 18.1 | l. (        | Overview                                         | 377 |

| 18.2 | 2. (        | Characteristics                                  |     |

| 18   | 3.2.1.      | SPI characteristics                              | 377 |

| 18   | 3.2.2.      | I2S characteristics                              | 377 |

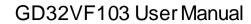

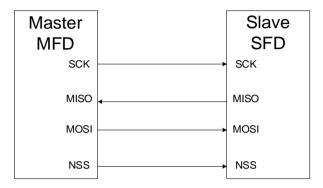

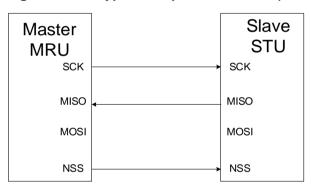

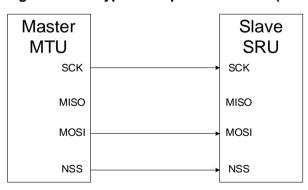

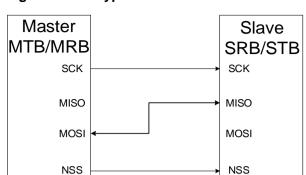

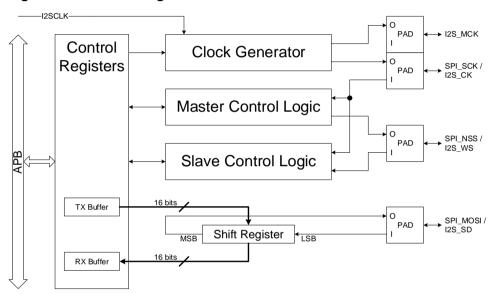

| 18.3 | 3. S        | PI block diagram                                 | 378 |

| 18.4 | ı. S        | PI signal description                            | 378 |

| 18   | 3.4.1.      | Normal configuration                             | 378 |

| 18.5 | 5. S        | PI function overview                             | 379 |

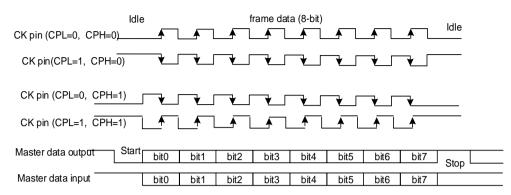

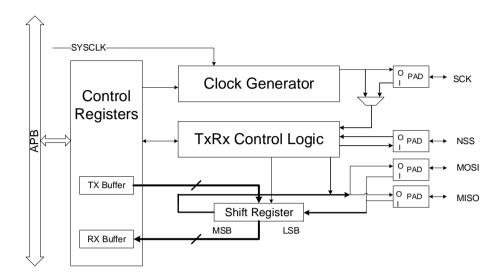

| 40   | 0 5 1       | SPI clock timing and data format                 | 270 |

| 18.5.2. NSS function                               | 379 |

|----------------------------------------------------|-----|

| 18.5.3. SPI operating modes                        | 380 |

| 18.5.4. DMA function                               | 386 |

| 18.5.5. CRC function                               | 386 |

| 18.6. SPI interrupts                               | 386 |

| 18.6.1. Status flags                               | 386 |

| 18.6.2. Error flags                                | 387 |

| 18.7. I2S block diagram                            | 388 |

| 18.8. I2S signal description                       | 388 |

| 18.9. I2S function overview                        | 389 |

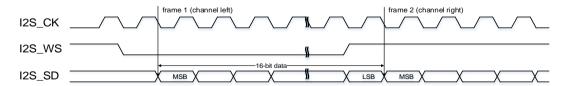

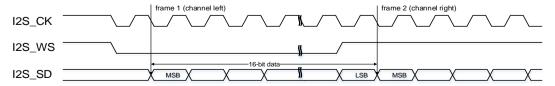

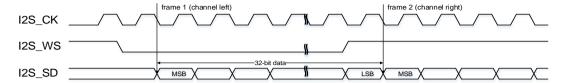

| 18.9.1. I2S audio standards                        | 389 |

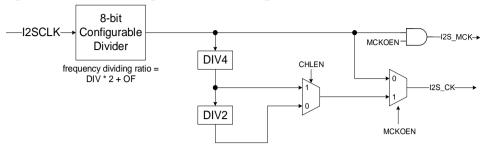

| 18.9.2. I2S clock                                  | 397 |

| 18.9.3. Operation                                  | 397 |

| 18.9.4. DMA function                               | 400 |

| 18.10. I2S interrupts                              | 400 |

| 18.10.1. Status flags                              | 400 |

| 18.10.2. Error flags                               | 401 |

| 18.11. Register definition                         | 403 |

| 18.11.1. Control register 0 (SPI_CTL0)             | 403 |

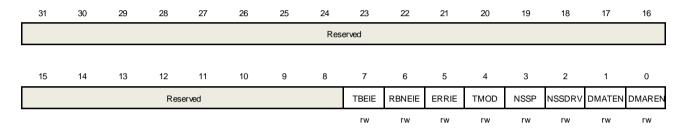

| 18.11.2. Control register 1 (SPI_CTL1)             | 405 |

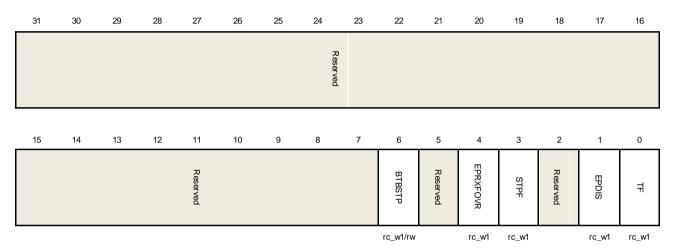

| 18.11.3. Status register (SPI_STAT)                | 406 |

| 18.11.4. Data register (SPI_DATA)                  | 407 |

| 18.11.5. CRC polynomial register (SPI_CRCPOLY)     |     |

| 18.11.6. RX CRC register (SPI_RCRC)                |     |

| 18.11.7. TX CRC register (SPI_TCRC)                |     |

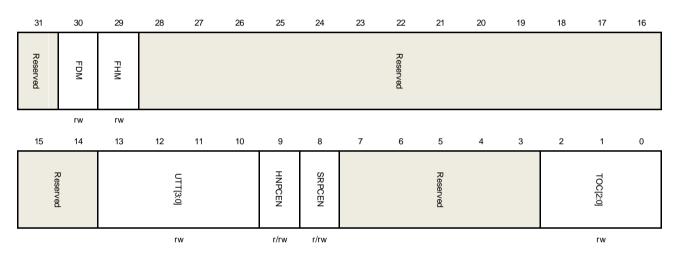

| 18.11.8. I2S control register (SPI_I2SCTL)         |     |

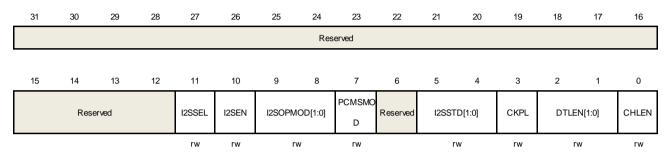

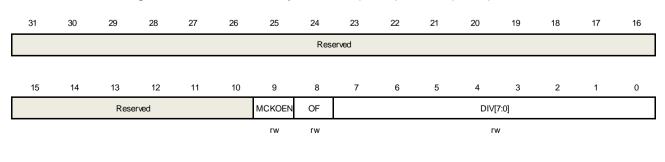

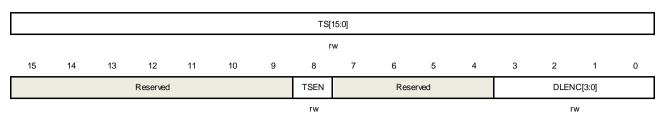

| 18.11.9. I2S clock prescaler register (SPI_I2SPSC) | 411 |

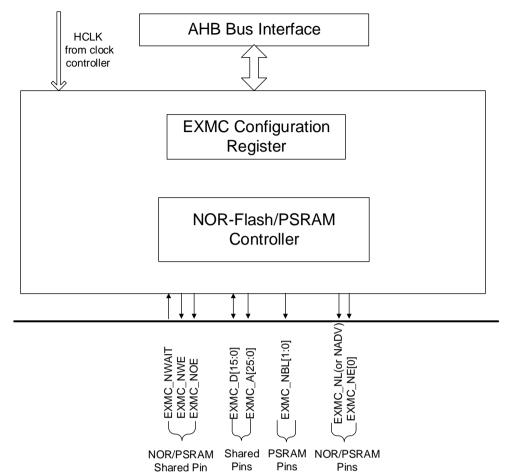

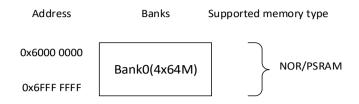

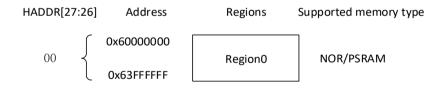

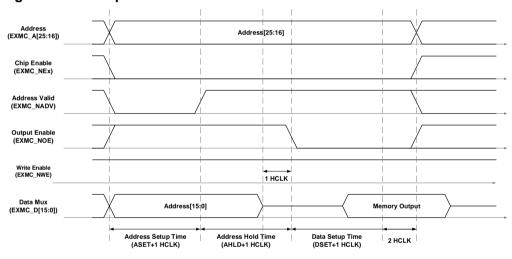

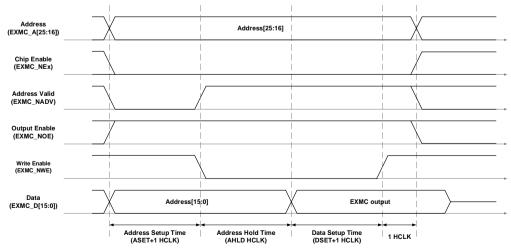

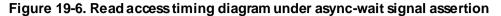

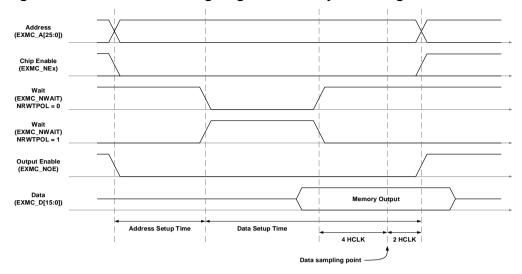

| 19. External memory controller (EXMC)              | 413 |

| 19.1. Overview                                     | 413 |

| 19.2. Characteristics                              | 413 |

| 19.3. Function overview                            | 413 |

| 19.3.1. Block diagram                              | 413 |

| 19.3.2. Basic regulation of EXMC access            | 414 |

| 19.3.3. External device address mapping            | 415 |

| 19.3.4. NOR/PSRAM controller                       | 415 |

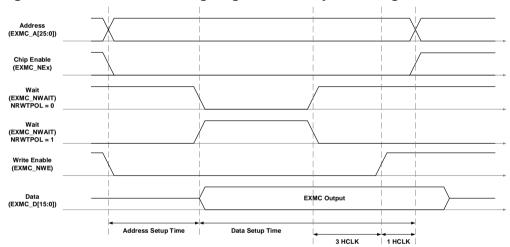

| 19.4. Register definition                          | 421 |

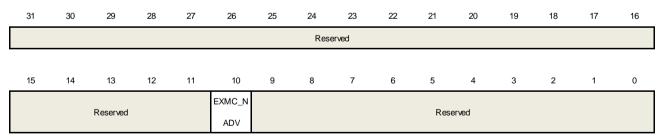

| 19.4.1. NOR/PSRAM controller registers             | 421 |

| 20. Controller area network (CAN)                  | 424 |

| 20.1. Overview                                     | 424 |

| 20.2.  | Characteristics                                                                    | 424 |

|--------|------------------------------------------------------------------------------------|-----|

| 20.3.  | Function overview                                                                  | 424 |

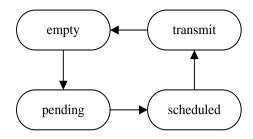

| 20.3.  | I. Working mode                                                                    | 425 |

| 20.3.2 | 2. Communication modes                                                             | 426 |

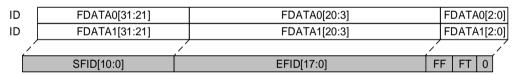

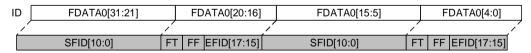

| 20.3.3 | 3. Data transmission                                                               | 427 |

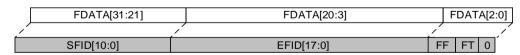

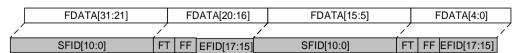

| 20.3.4 | 4. Data reception                                                                  | 429 |

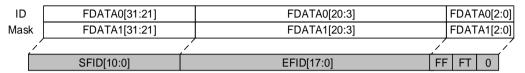

| 20.3.  | 5. Filtering function                                                              | 430 |

| 20.3.6 | 6. Time-triggered communication                                                    | 433 |

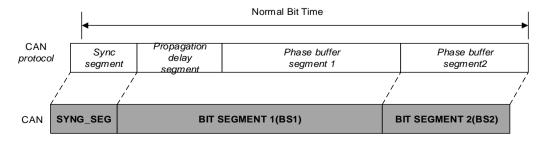

| 20.3.  | 7. Communication parameters                                                        | 433 |

| 20.3.8 | 3. Error flags                                                                     | 435 |

| 20.3.9 | O. CAN interrupts                                                                  | 436 |

| 20.4.  | Register definition                                                                | 438 |

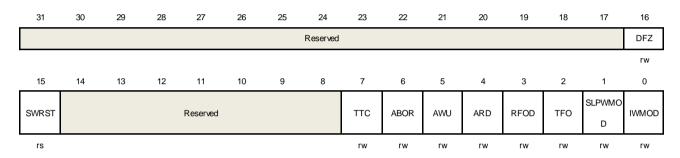

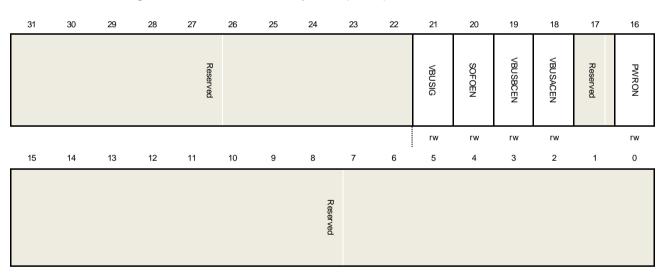

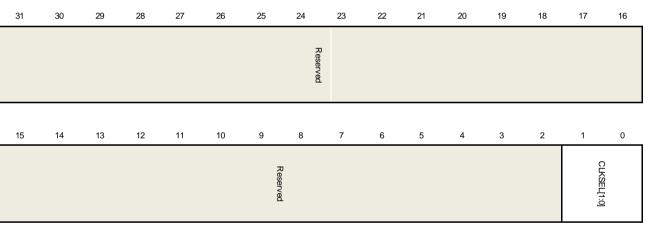

| 20.4.  | Control register (CAN_CTL)                                                         | 438 |

| 20.4.2 | 2. Status register (CAN_STAT)                                                      | 439 |

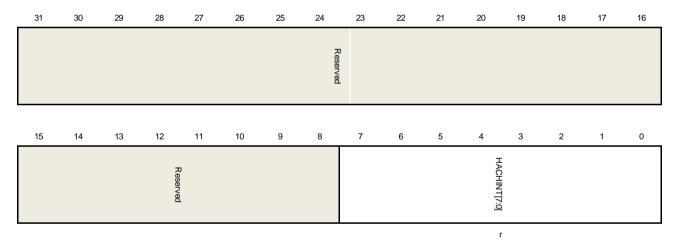

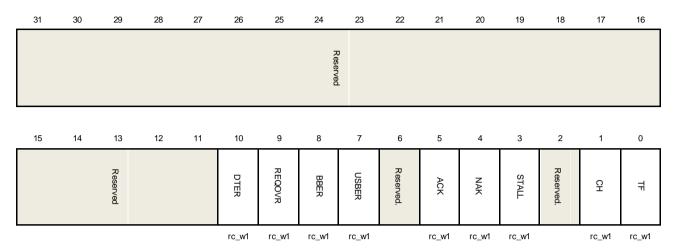

| 20.4.3 | 3. Transmit status register (CAN_TSTAT)                                            | 441 |

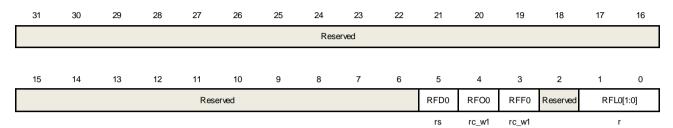

| 20.4.4 | 4. Receive message FIFO0 register (CAN_RFIFO0)                                     | 444 |

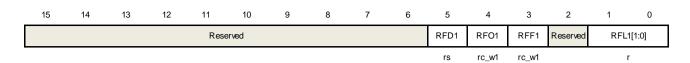

| 20.4.  | 5. Receive message FIFO1 register (CAN_RFIFO1)                                     | 444 |

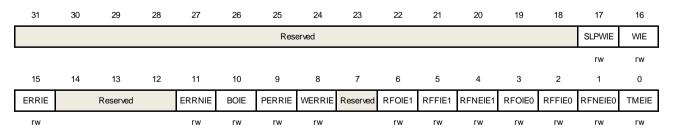

| 20.4.6 | 6. Interrupt enable register (CAN_INTEN)                                           | 445 |

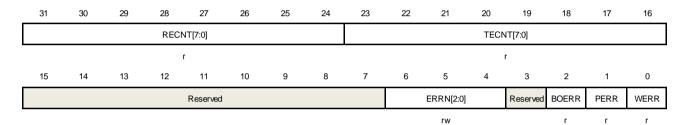

| 20.4.  | 7. Error register (CAN_ERR)                                                        | 447 |

| 20.4.8 | 3. Bit timing register (CAN_BT)                                                    | 448 |

| 20.4.9 | 9. Transmit mailbox identifier register (CAN_TMk) (x=02)                           | 449 |

| 20.4.  | 10. Transmit mailbox property register (CAN_TMPx) (x=02)                           | 449 |

| 20.4.  | 11. Transmit mailbox data0 register (CAN_TMDATA0x) (x=02)                          | 450 |

| 20.4.  | 12. Transmit mailbox data1 register (CAN_TMDATA1x) (x=02)                          | 451 |

| 20.4.  | 13. Receive FIFO mailbox identifier register (CAN_RFIFOMIx) (x=0,1)                | 451 |

| 20.4.  | 14. Receive FIFO mailbox property register (CAN_RFIFOMPx) (x=0,1)                  | 452 |

| 20.4.  | 15. Receive FIFO mailbox data0 register (CAN_RFIFOMDATA0x) (x=0,1)                 | 453 |

| 20.4.  | <ol> <li>Receive FIFO mailbox data1 register (CAN_RFIFOMDATA1x) (x=0,1)</li> </ol> | 453 |

| 20.4.  | 9 ( = /( /                                                                         |     |

| 20.4.  |                                                                                    |     |

| 20.4.  |                                                                                    |     |

| 20.4.2 |                                                                                    |     |

| 20.4.2 |                                                                                    |     |

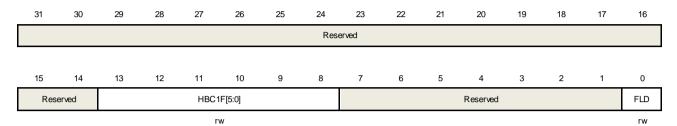

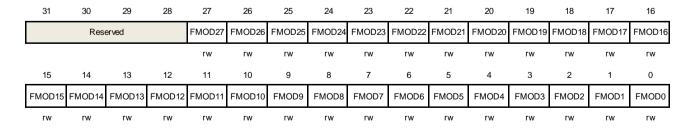

| 20.4.2 | 22. Filter x data y register (CAN_FxDATAy) (x=027, y=0,1) (Just for CAN0)          | 456 |

| 21. Un | iversal serial bus full-speed interface (USBFS)                                    | 458 |

| 21.1.  | Overview                                                                           | 458 |

| 21.2.  | Characteristics                                                                    | 458 |

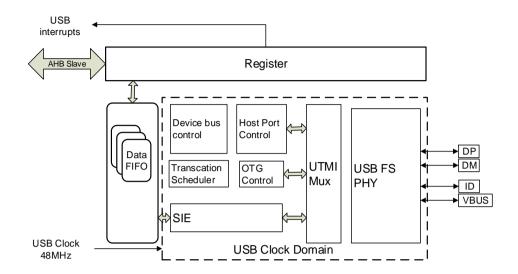

| 21.3.  | Block diagram                                                                      | 459 |

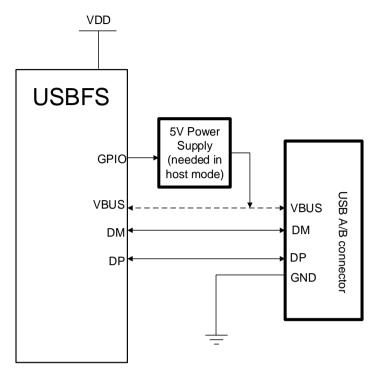

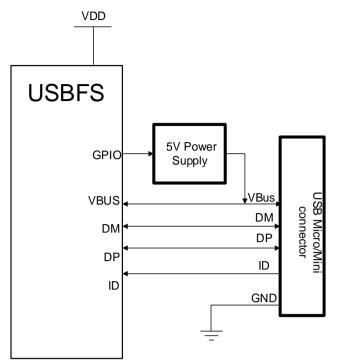

| 21.4.  | Signal description                                                                 | 459 |

| 21.5.  | Function overview                                                                  | 459 |

|        | L USBFS clocks and working modes                                                   |     |

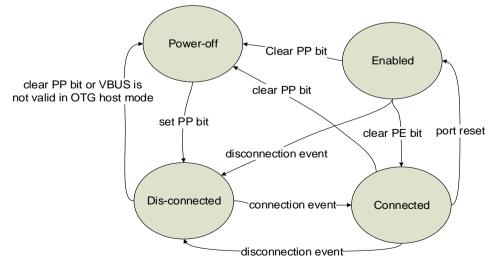

| 21.5.2. | USB host function                                  | 461 |

|---------|----------------------------------------------------|-----|

| 21.5.3. |                                                    |     |

| 21.5.4. |                                                    |     |

| 21.5.5. |                                                    |     |

| 21.5.6. |                                                    |     |

| 21.6.   | Interrupts                                         |     |

| 21.7.   | Register definition                                | 474 |

| 21.7.1. | Global control and status registers                | 474 |

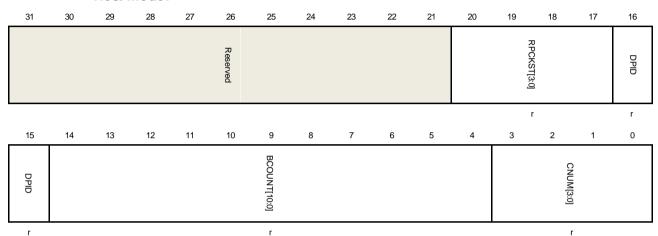

| 21.7.2. | Host control and status registers                  | 495 |

| 21.7.3. | Device control and status registers                | 507 |

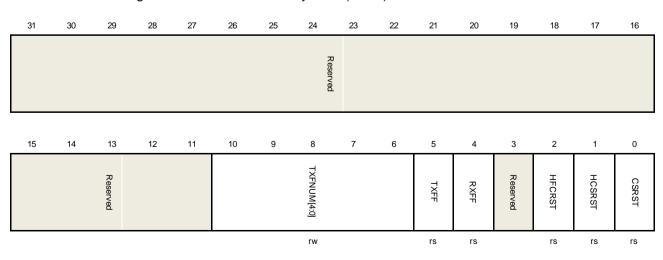

| 21.7.4. | Power and clock control register (USBFS_PWRCLKCTL) | 530 |

| 22. App | endix                                              | 532 |

| 22.1.   | List of abbreviations used in register             | 532 |

| 22.2.   | List of terms                                      | 532 |

| 22.3.   | Available peripherals                              | 533 |

| 23. Rev | rision history                                     | 533 |

# **List of Figures**

| Figure 1-1. GD32VF103 system architecture                                    | 24  |

|------------------------------------------------------------------------------|-----|

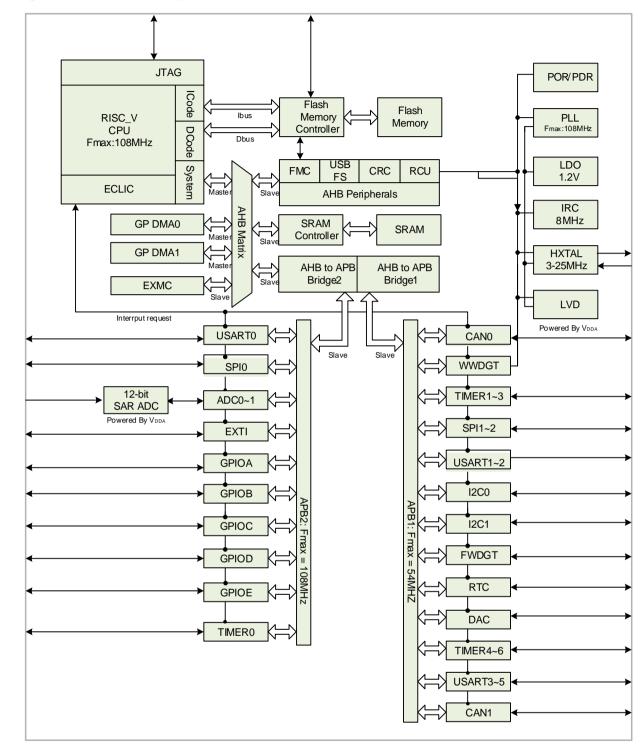

| Figure 2-1. Process of page erase operation                                  | 34  |

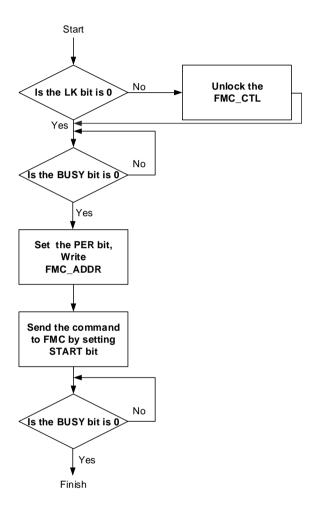

| Figure 2-2 Process of mass erase operation                                   | 35  |

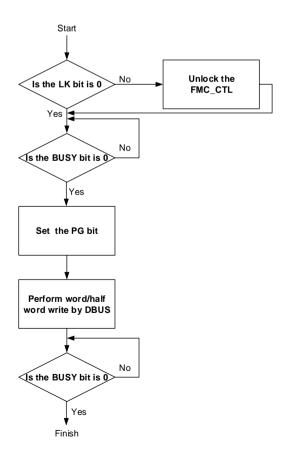

| Figure 2-3. Process of word program operation                                | 36  |

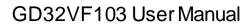

| Figure 3-1. Power supply overview                                            |     |

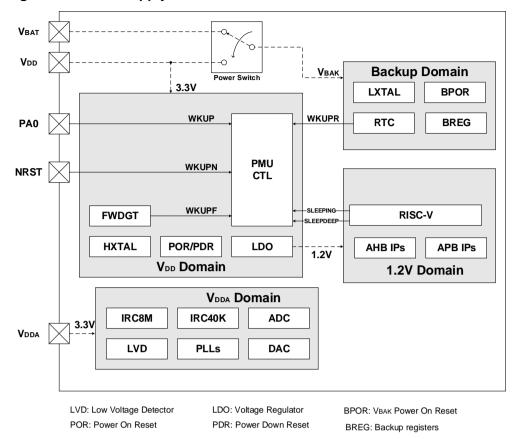

| Figure 3-2. Waveform of the POR/PDR                                          | 49  |

| Figure 3-3. Waveform of the LVD threshold                                    | 49  |

| Figure 5-1. The system reset circuit                                         | 62  |

| Figure 5-2 Clock tree                                                        | 63  |

| Figure 5-3. HXTAL clock source                                               | 64  |

| Figure 6-1. Block diagram of EXTI                                            | 96  |

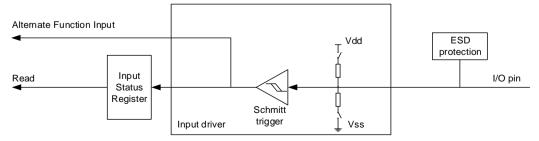

| Figure 7.1. Basic structure of a standard I/O port bit                       | 102 |

| Figure 7.2. Input configuration                                              | 103 |

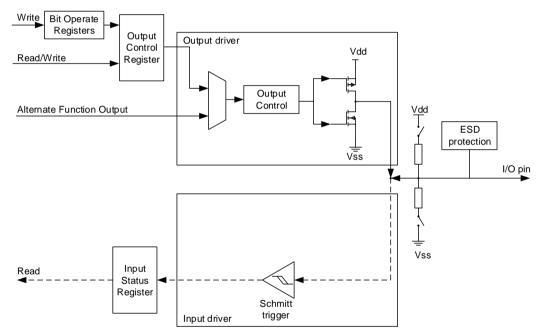

| Figure 7.3. Output configuration                                             | 104 |

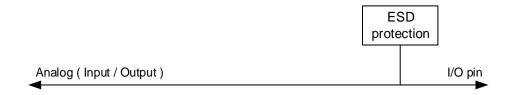

| Figure 7.4. Analog configuration                                             | 104 |

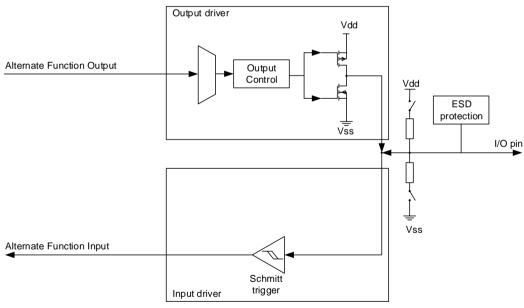

| Figure 7.5. Alternate function configuration                                 | 105 |

| Figure 8-1. Block diagram of CRC calculation unit                            | 127 |

| Figure 9-1. Block diagram of DMA                                             | 132 |

| Figure 9-2. Handshake mechanism                                              | 134 |

| Figure 9-3. DMA interrupt logic                                              | 136 |

| Figure 9-4. DMA0 request mapping                                             | 137 |

| Figure 9-5. DMA1 request mapping                                             | 138 |

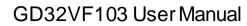

| Figure 11-1. ADC module block diagram                                        | 152 |

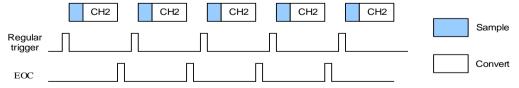

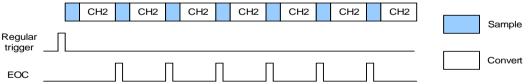

| Figure 11-2 Single conversion mode                                           | 154 |

| Figure 11-3. Continuous conversion mode                                      | 155 |

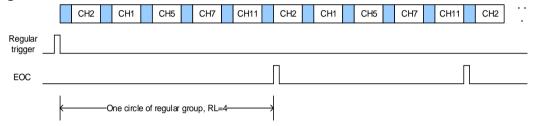

| Figure 11-4. Scan conversion mode, continuous disable                        | 156 |

| Figure 11-5. Scan conversion mode, continuous enable                         | 157 |

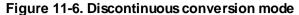

| Figure 11-6. Discontinuous conversion mode                                   | 158 |

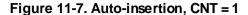

| Figure 11-7. Auto-insertion, CNT = 1                                         | 159 |

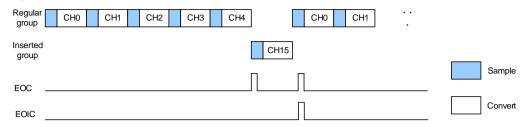

| Figure 11-8. Triggered insertion                                             | 159 |

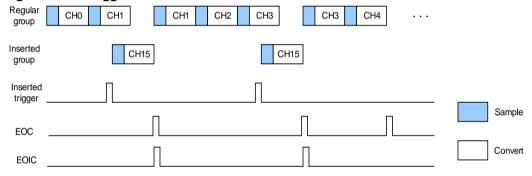

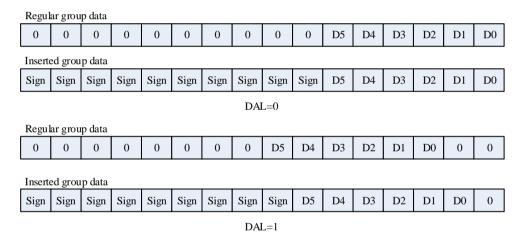

| Figure 11-9. 12-bit Data alignment                                           | 160 |

| Figure 11-10. 6-bit Data alignment                                           | 160 |

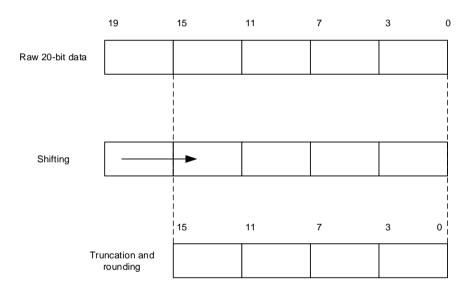

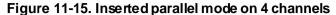

| Figure 11-11. 20-bit to 16-bit result truncation                             | 163 |

| Figure 11-12. Numerical example with 5-bits shift and rounding               | 164 |

| Figure 11-13. ADC sync block diagram                                         | 165 |

| Figure 11-14. Regular parallel mode on 16 channels                           | 166 |

| Figure 11-15. Inserted parallel mode on 4 channels                           | 167 |

| Figure 11-16. Follow-up fast mode on 1 channel in continuous conversion mode | 167 |

| Figure 11-17. Follow-up slow mode on 1 channel                               |     |

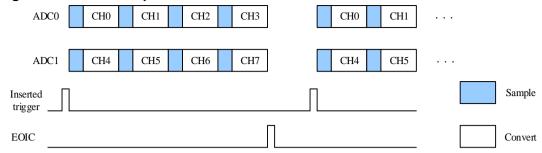

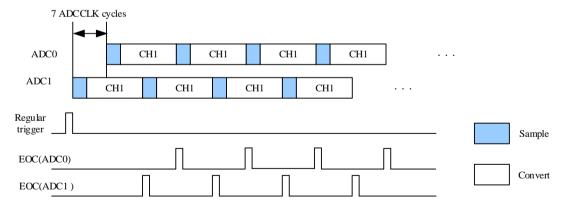

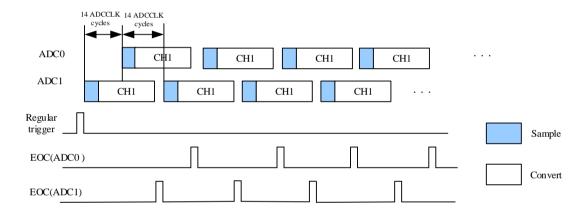

| Figure 11-18. Trigger rotation: inserted channel group                       | 169 |

| Figure 11-19. Trigger rotation: inserted channels in discontinuous modemode  | 169 |

| Figure 11-20. Regular parallel & trigger rotation mode                                      |     |

|---------------------------------------------------------------------------------------------|-----|

| Figure 11-21. Trigger occurs during inserted conversion                                     | 170 |

| Figure 11-22 Follow-up single channel with inserted sequence CH1, CH2                       | 171 |

| Figure 12-1. DAC block diagram                                                              | 187 |

| Figure 12-2 DAC LFSR algorithm                                                              | 189 |

| Figure 12-3. DAC triangle noise wave                                                        | 189 |

| Figure 13.1. Free watchdog block diagram                                                    | 201 |

| Figure 13.2. Window watchdog timer block diagram                                            | 207 |

| Figure 13.3. Window watchdog timing diagram                                                 | 208 |

| Figure 14.1. Block diagram of RTC                                                           | 212 |

| Figure 14.2. RTC second and alarm waveform example (RTC_PSC = 3, RTC_ALRM = 2)              | 213 |

| Figure 14.3. RTC second and overflow waveform example (RTC_PSC= 3)                          | 214 |

| Figure 15-1. Advanced timer block diagram                                                   | 222 |

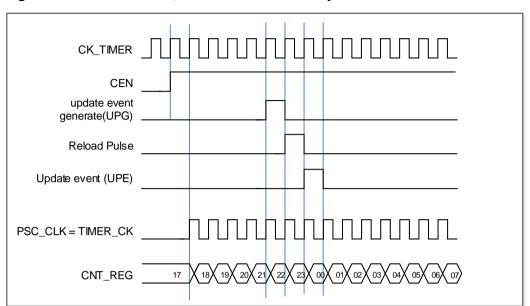

| Figure 15-2. Normal mode, internal clock divided by 1                                       | 223 |

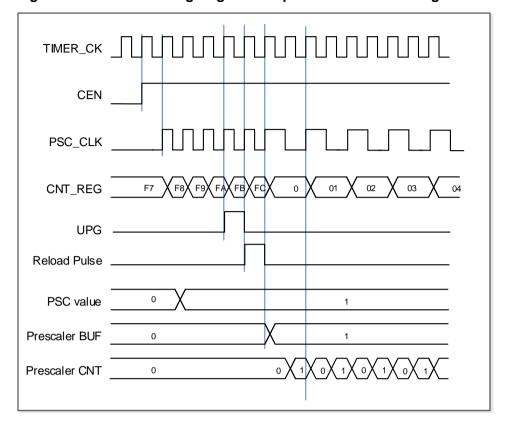

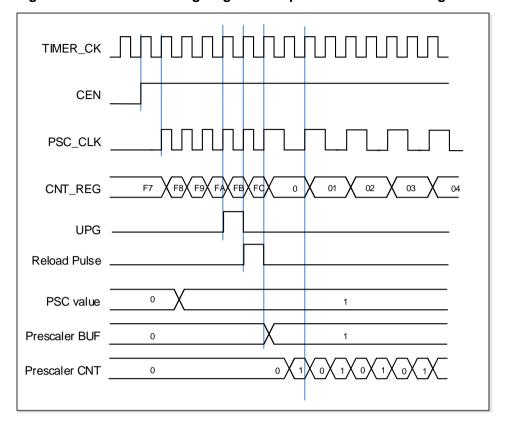

| Figure 15-3. Counter timing diagram with prescaler division change from 1 to 2 1 to 2       | 224 |

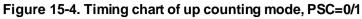

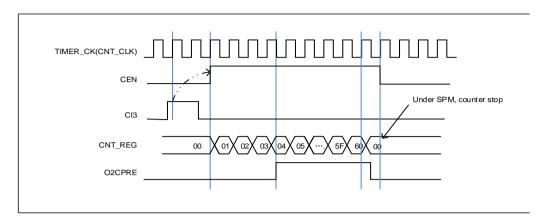

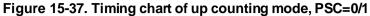

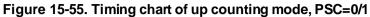

| Figure 15-4. Timing chart of up counting mode, PSC=0/1                                      | 225 |

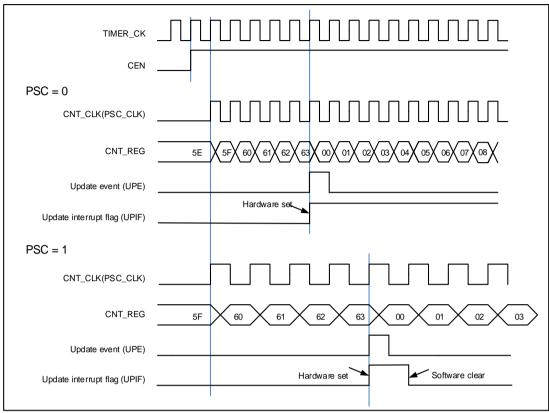

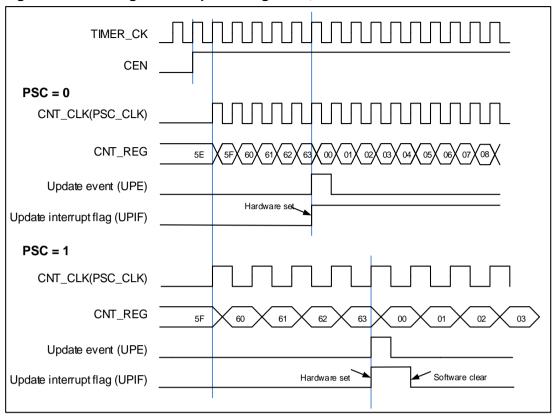

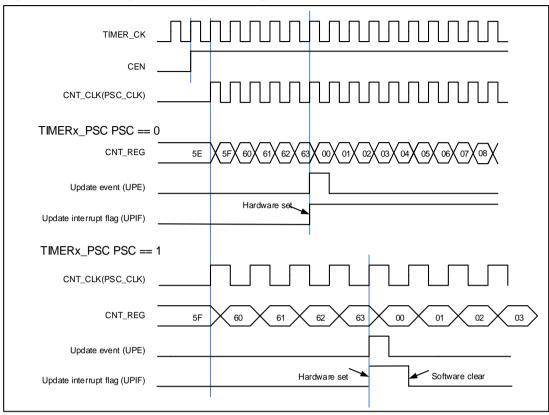

| Figure 15-5. Timing chart of up counting mode, change TIMERx_CAR ongoing                    | 226 |

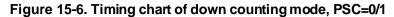

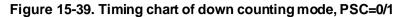

| Figure 15-6. Timing chart of down counting mode, PSC=0/1                                    | 227 |

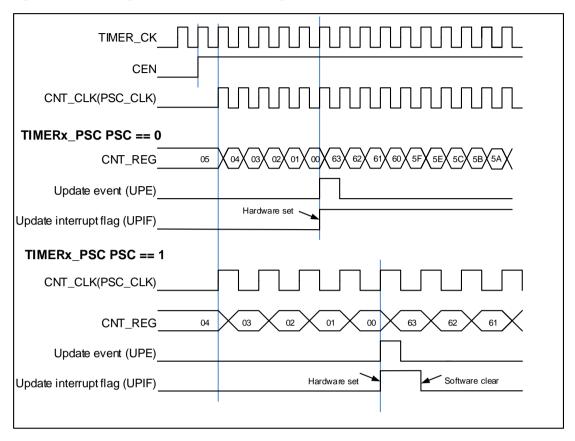

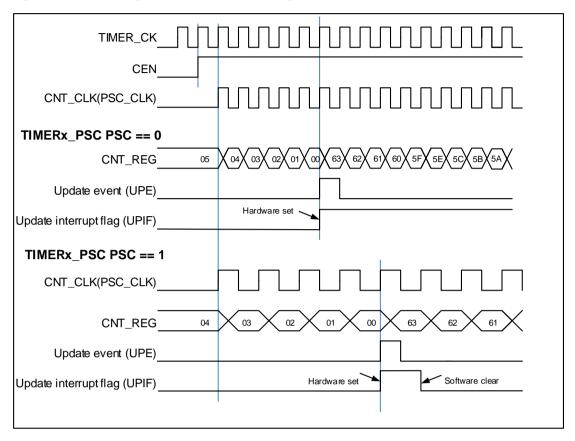

| Figure 15-7. Timing chart of down counting mode, change TIMERx_CAR ongoing                  | 228 |

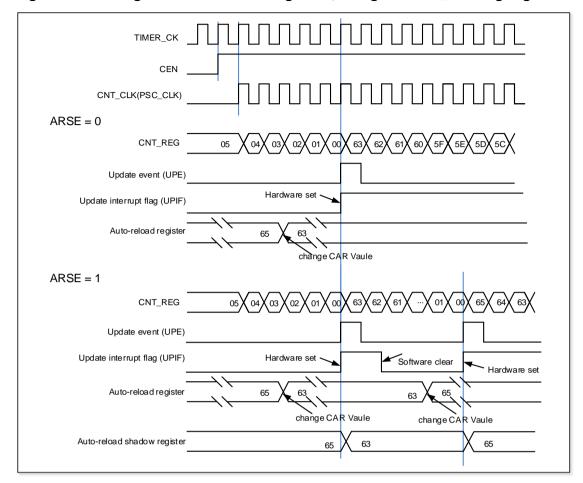

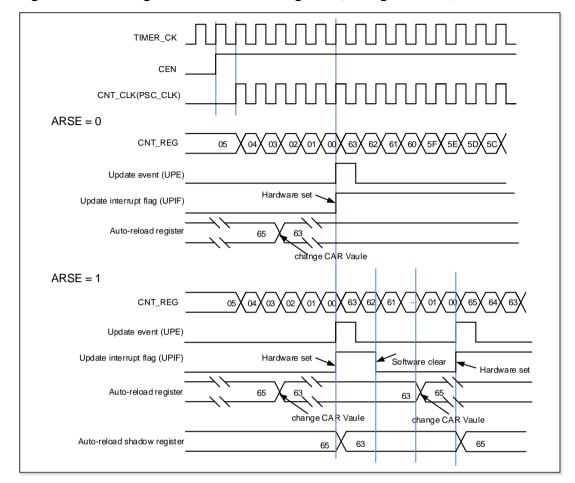

| Figure 15-8. Timing chart of center-aligned counting mode                                   | 229 |

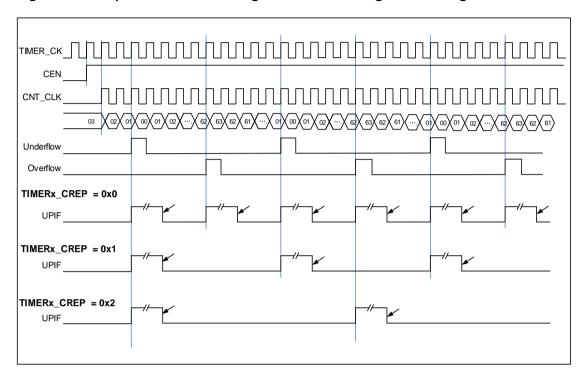

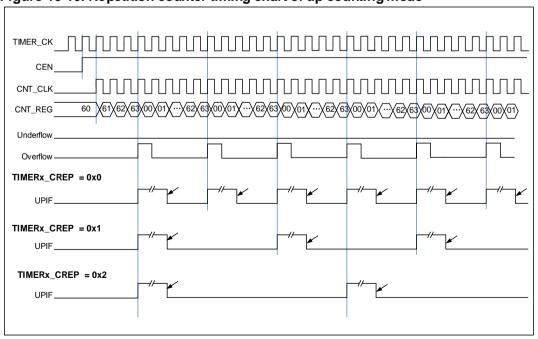

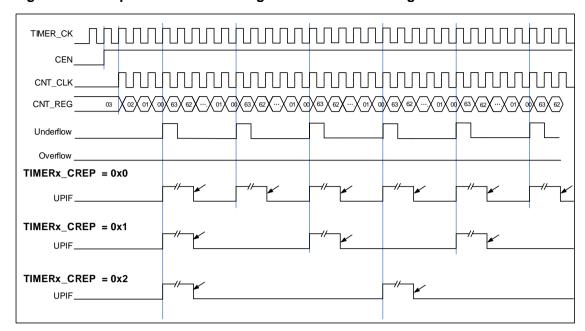

| Figure 15-9. Repetition counter timing chart of center-aligned counting modemode            | 230 |

| Figure 15-10. Repetition counter timing chart of up counting modemode                       | 230 |

| Figure 15-11. Repetition counter timing chart of down counting modemode                     |     |

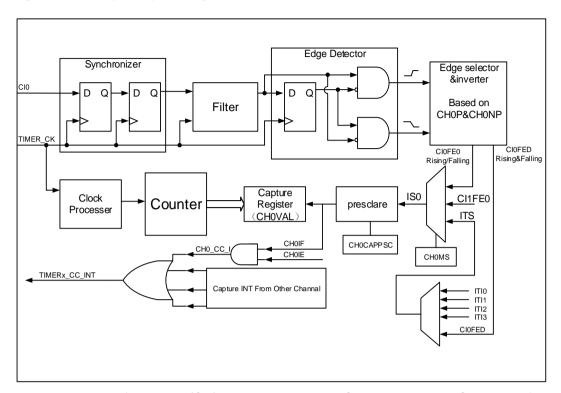

| Figure 15-12 Input capture logic                                                            | 232 |

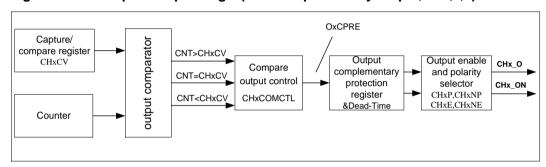

| Figure 15-13. Output compare logic (with complementary output, x=0,1,2)                     | 233 |

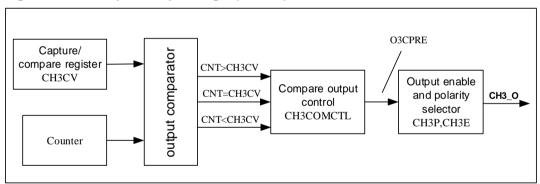

| Figure 15-14. Output compare logic (CH3_O)                                                  | 233 |

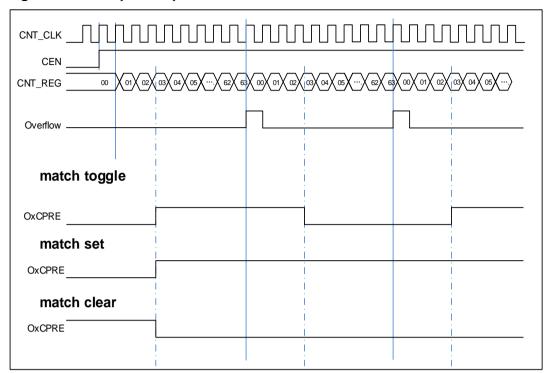

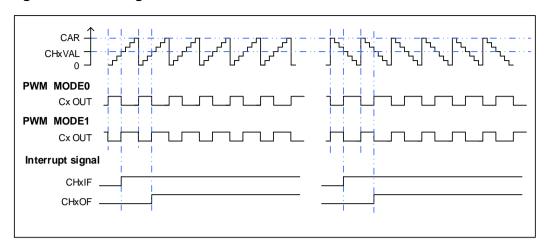

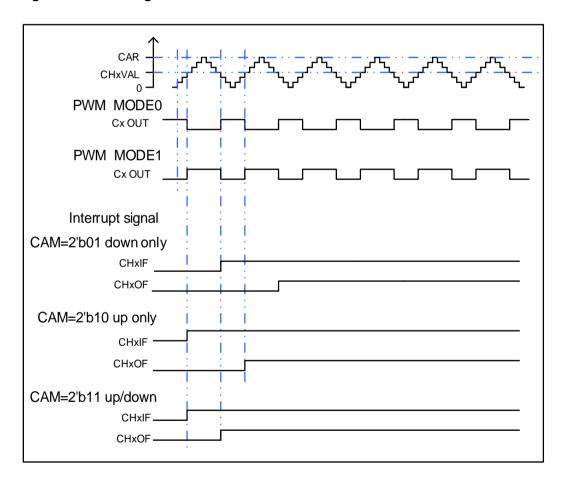

| Figure 15-15. Output-compare in three modes                                                 | 235 |

| Figure 15-16. Timing chart of EAPWM                                                         | 236 |

| Figure 15-17. Timing chart of CAPWM                                                         | 236 |

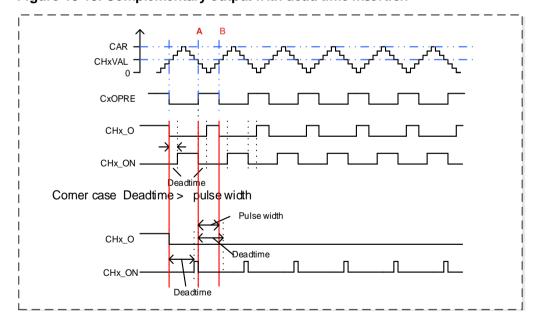

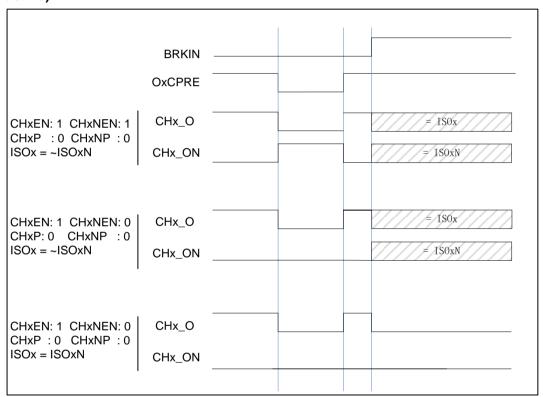

| Figure 15-18. Complementary output with dead time insertion                                 | 239 |

| Figure 15-19. Output behavior of the channel in response to a break (the break high active) | 240 |

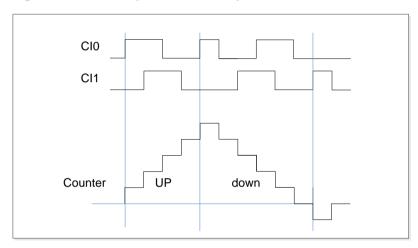

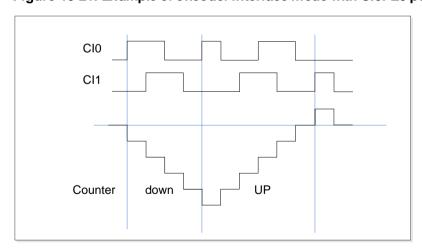

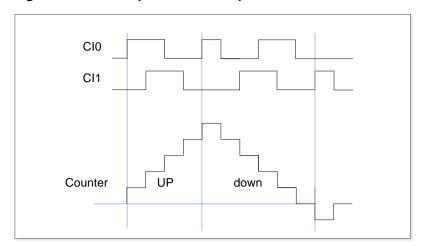

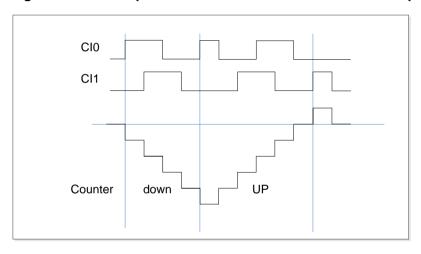

| Figure 15-20. Example of counter operation in encoder interface mode                        | 241 |

| Figure 15-21. Example of encoder interface mode with Cl0FE0 polarity inverted               | 241 |

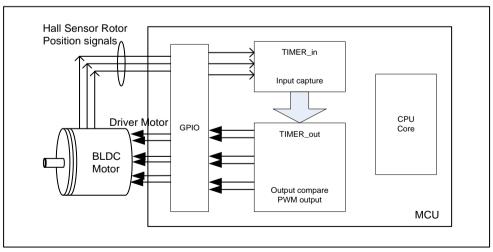

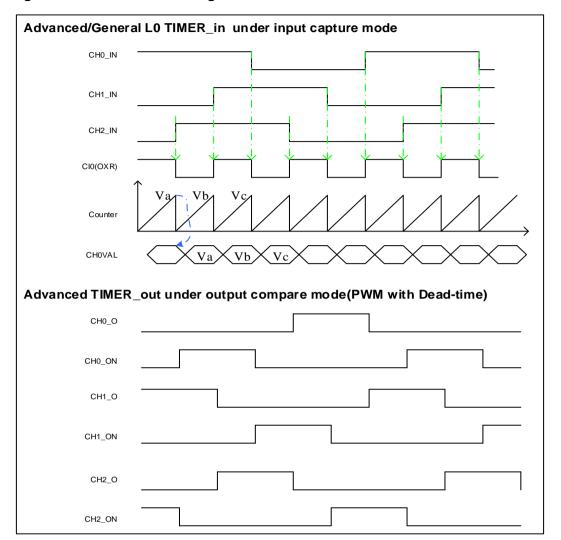

| Figure 15-22. Hall sensor is used to BLDC motor                                             | 242 |

| Figure 15-23. Hall sensor timing between two timers                                         | 243 |

| Figure 15-24. Restart mode                                                                  |     |

| Figure 15-25. Pause mode                                                                    | 244 |

| Figure 15-26. Event mode                                                                    | 245 |

| Figure 15-27. Single pulse mode TIMERx_CHxCV=0x04, TIMERx_CAR=0x60                          | 246 |

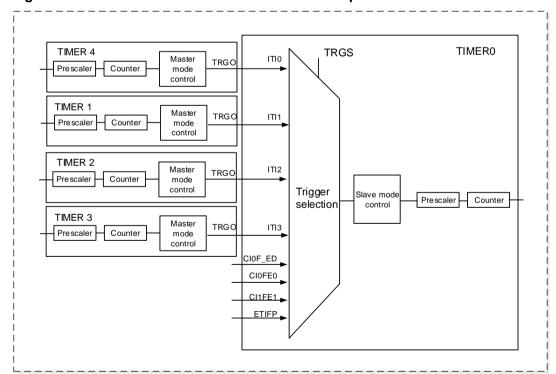

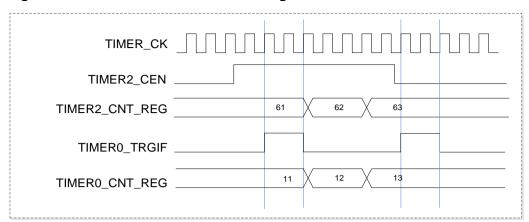

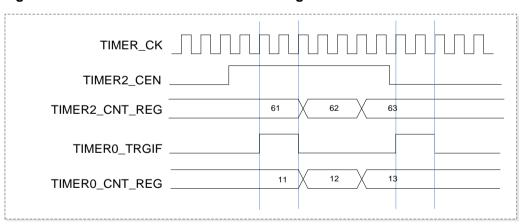

| Figure 15-28. TIMER0 Master/Slave mode timer example                                        |     |

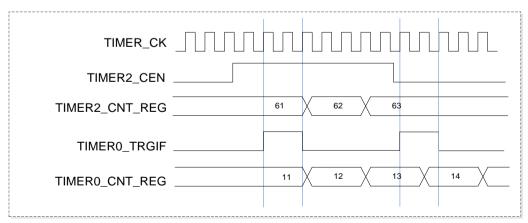

| Figure 15-29. Triggering TIMER0 with enable signal of TIMER2                                |     |

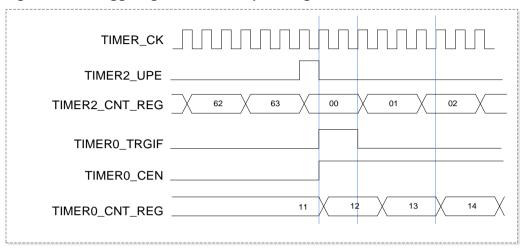

| Figure 15-30. Triggering TIMER0 with update signal of TIMER2                                |     |

| Figure 15-31. Pause TIMER0 with enable signal of TIMER2                                     |     |

| Figure 15-32 Pause TIMER0 with O0CPREF signal of Timer2                                     |     |

| Figure 15-33. Triggering TIMER0 and TIMER2 with TIMER2's CIO input              | 250 |

|---------------------------------------------------------------------------------|-----|

| Figure 15-34. General Level 0 timer block diagram                               | 278 |

| Figure 15-35. Normal mode, internal clock divided by 1                          | 279 |

| Figure 15-36. Counter timing diagram with prescaler division change from 1 to 2 | 280 |

| Figure 15-37. Timing chart of up counting mode, PSC=0/1                         | 281 |

| Figure 15-38. Timing chart of up counting mode, change TIMERx_CAR ongoing       | 282 |

| Figure 15-39. Timing chart of down counting mode, PSC=0/1                       | 283 |

| Figure 15-40. Timing chart of down counting mode, change TIMERx_CAR             | 284 |

| Figure 15-41. Timing chart of center-aligned counting mode                      | 285 |

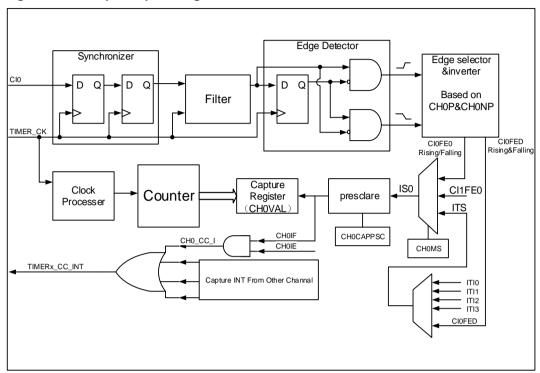

| Figure 15-42 Input capture logic                                                | 286 |

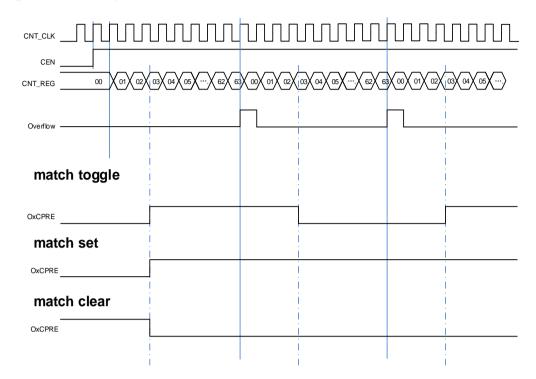

| Figure 15-43. Output-compare in three modes                                     | 288 |

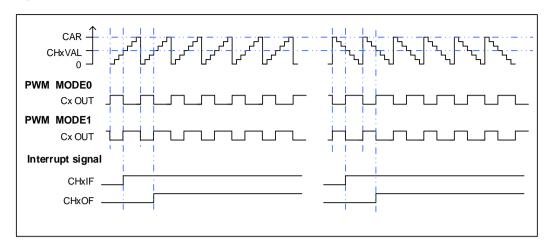

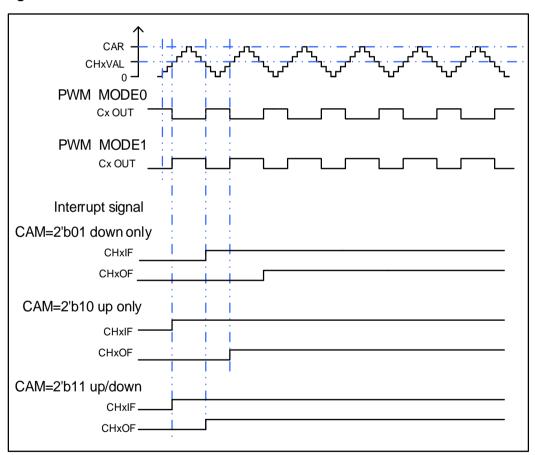

| Figure 15-44. EAPWM timechart                                                   | 289 |

| Figure 15-45. CAPWM timechart                                                   | 289 |

| Figure 15-46. Example of counter operation in encoder interface mode            | 291 |

| Figure 15-47. Example of encoder interface mode with Cl0FE0 polarity inverted   | 291 |

| Figure 15-48. Restart mode                                                      | 292 |

| Figure 15-49. Pause mode                                                        | 292 |

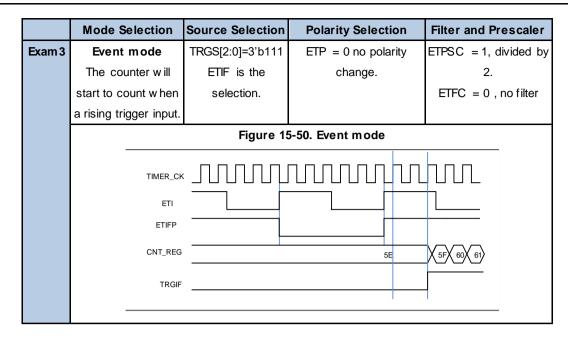

| Figure 15-50. Event mode                                                        | 293 |

| Figure 15-51. Single pulse mode TIMERx_CHxCV = 0x04 TIMERx_CAR=0x60             | 294 |

| Figure 15-52. Basic timer block diagram                                         | 315 |

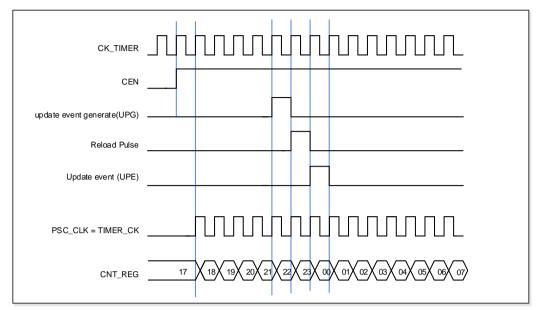

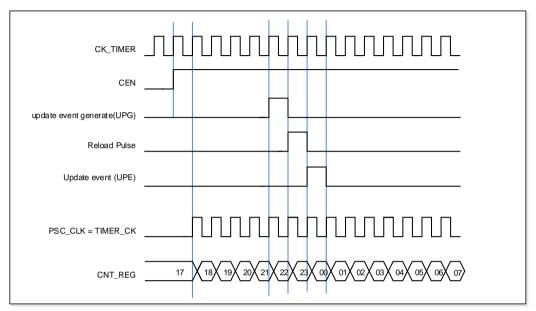

| Figure 15-53. Normal mode, internal clock divided by 1                          | 316 |

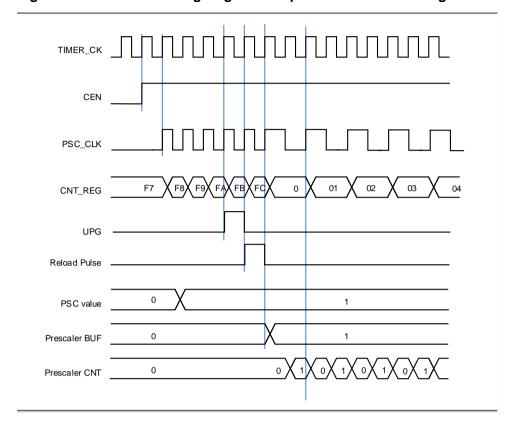

| Figure 15-54. Counter timing diagram with prescaler division change from 1 to 2 | 317 |

| Figure 15-55. Timing chart of up counting mode, PSC=0/1                         | 318 |

| Figure 15-56. Timing chart of up counting mode, change TIMERx_CAR ongoing       | 319 |

| Figure 16-1. USART module block diagram                                         | 327 |

| Figure 16-2. USART character frame (8 bits data and 1 stop bit)                 |     |

| Figure 16-3. USART transmit procedure                                           |     |

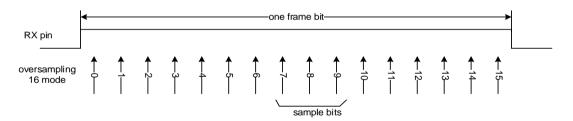

| Figure 16-4. Receiving a frame bit by oversampling method                       | 330 |

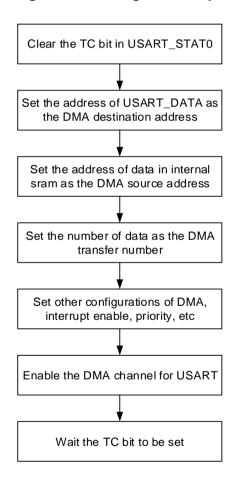

| Figure 16-5. Configuration steps when using DMA for USART transmission          | 331 |

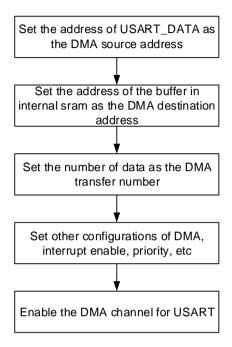

| Figure 16-6. Configuration steps when using DMA for USART reception             |     |

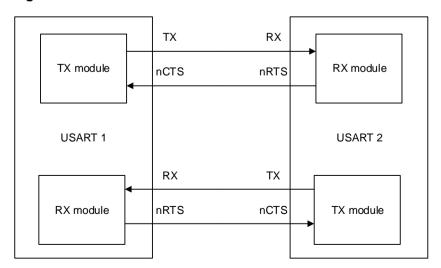

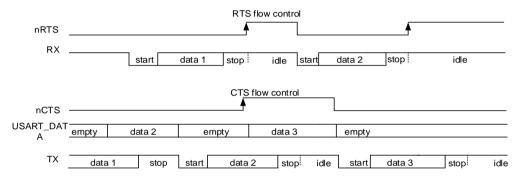

| Figure 16-7. Hardware flow control between two USARTs                           | 332 |

| Figure 16-8. Hardware flow control                                              | 333 |

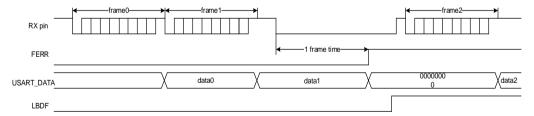

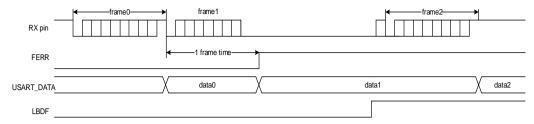

| Figure 16-9. Break frame occurs during idle state                               | 334 |

| Figure 16-10. Break frame occurs during a frame                                 | 335 |

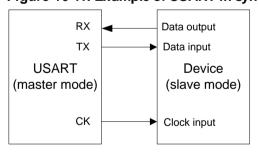

| Figure 16-11. Example of USART in synchronous mode                              | 335 |

| Figure 16-12. 8-bit format USART synchronous waveform (CLEN=1)                  | 336 |

| Figure 16-13. IrDA SIR ENDEC module                                             | 336 |

| Figure 16-14. IrDA data modulation                                              | 337 |

| Figure 16-15. ISO7816-3 frame format                                            |     |

| Figure 16-16. USART interrupt mapping diagram                                   |     |

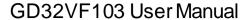

| Figure 17-1. I2C module block diagram                                           | 351 |

| Figure 17-2. Data validation                                                    |     |

| Figure 17-3. START and STOP condition                                           | 352 |

| Figure 17-4. Clock synchronization                                              |     |

| Figure 17-5. SDA Line arbitration                                                           | 353          |

|---------------------------------------------------------------------------------------------|--------------|

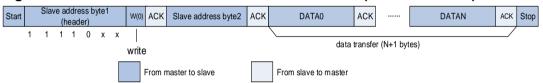

| Figure 17-6. I2C communication flow with 7-bit address                                      | 354          |

| Figure 17-7. I2C communication flow with 10-bit address (Master Transmit)                   | 354          |

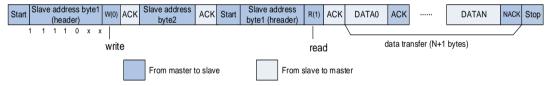

| Figure 17-8. I2C communication flow with 10-bit address (Master Receive)                    | 354          |

| Figure 17-9. Programming model for slave transmitting(10-bit address mode)                  | 356          |

| Figure 17-10. Programming model for slave receiving(10-bit address mode)                    | 357          |

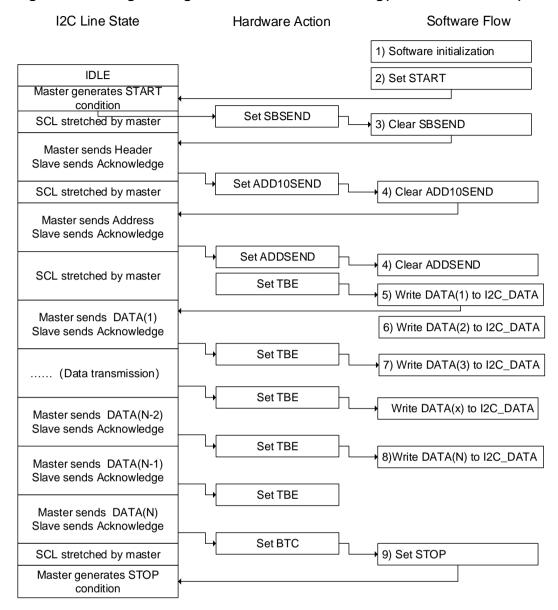

| Figure 17-11. Programming model for master transmitting(10-bit address mode)                | 359          |

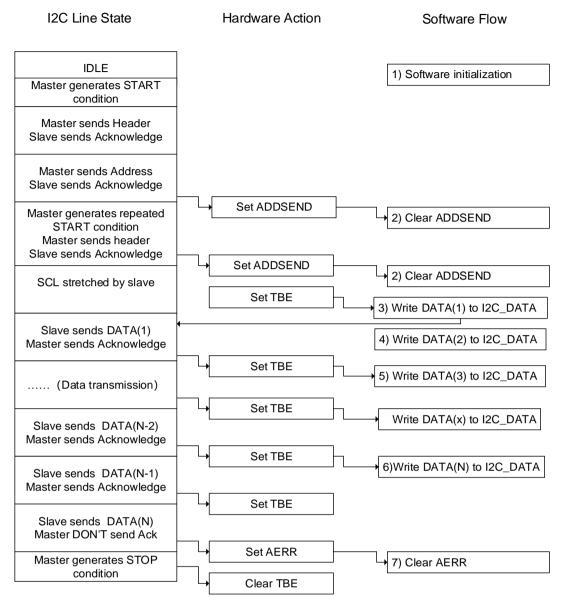

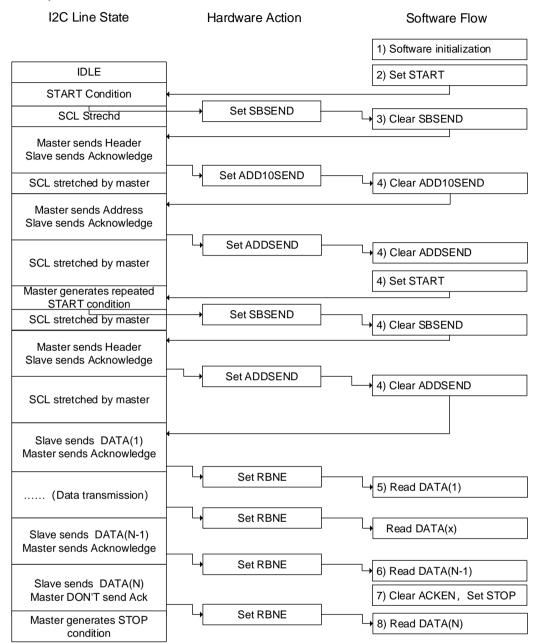

| Figure 17-12. Programming model for master receiving using Solution A(10-bit address model  | <b>∍)361</b> |

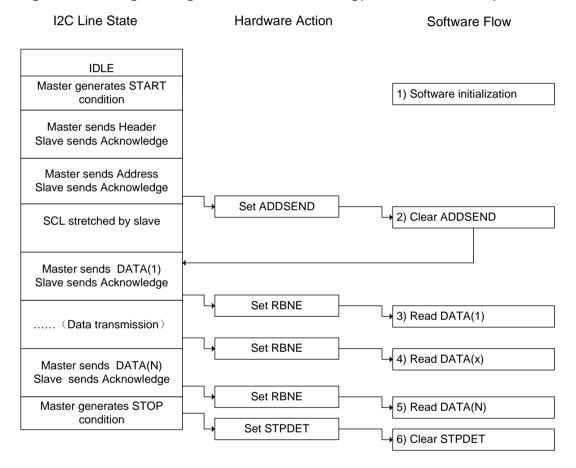

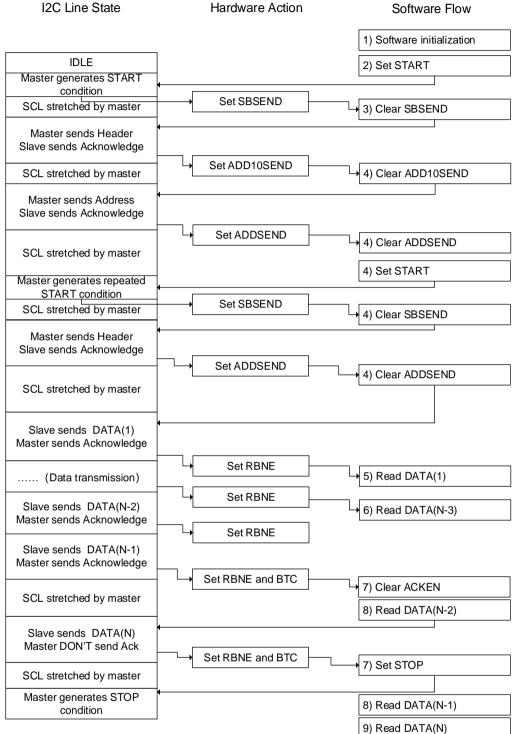

| Figure 17-13. Programming model for master receiving using solution B(10-bit address model) | ;)363        |

| Figure 18-1. Block diagram of SPI                                                           | 378          |

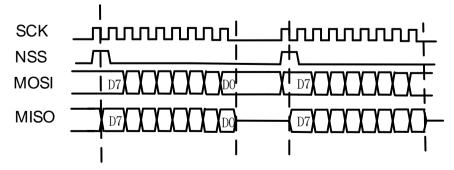

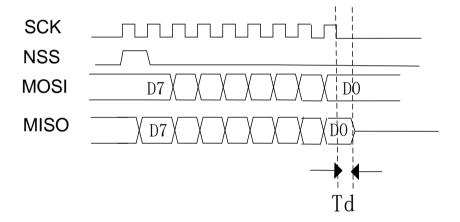

| Figure 18-2 SPI timing diagram in normal mode                                               | 379          |

| Figure 18-3. A typical full-duplex connection                                               | 381          |

| Figure 18-4. A typical simplex connection (Master: Receive, Slave: Transmit)                | 381          |

| Figure 18-5. A typical simplex connection (Master: Transmit only, Slave: Receive)           | 381          |

| Figure 18-6. A typical bidirectional connection                                             | 382          |

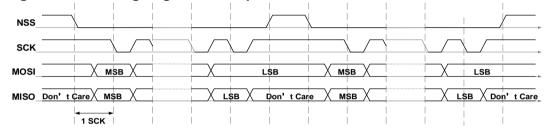

| Figure 18-7. Timing diagram of TI master mode with discontinuous transfer                   | 383          |

| Figure 18-8. Timing diagram of TI master mode with continuous transfer                      | 384          |

| Figure 18-9. Timing diagram of TI slave mode                                                | 384          |

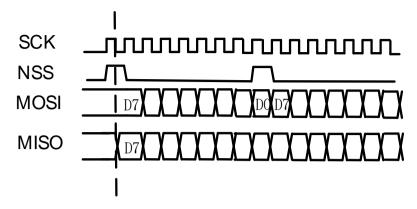

| Figure 18-10. Timing diagram of NSS pulse with continuous transmission                      | 385          |

| Figure 18-11. Block diagram of I2S                                                          | 388          |

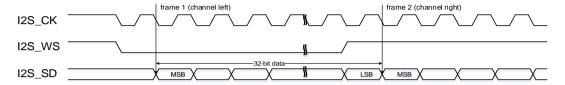

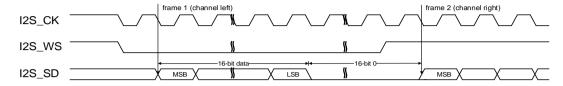

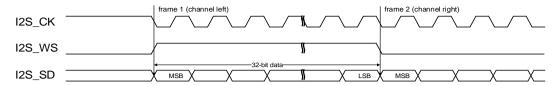

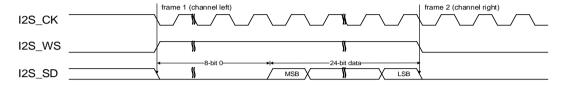

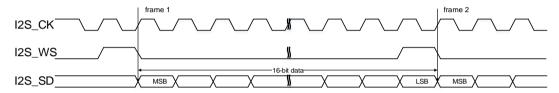

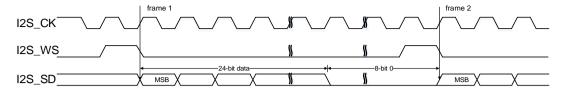

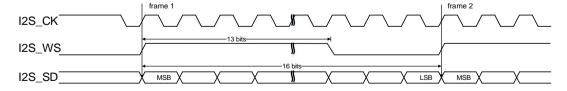

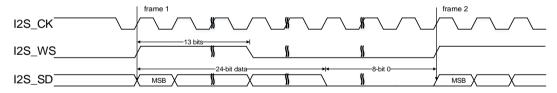

| Figure 18-12. I2S Phillips standard timing diagram (DTLEN=00, CHLEN=0, CKPL=0)              | 389          |

| Figure 18-13. I2S Phillips standard timing diagram (DTLEN=00, CHLEN=0, CKPL=1)              | 389          |

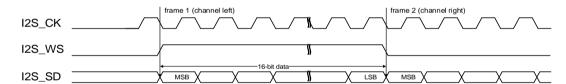

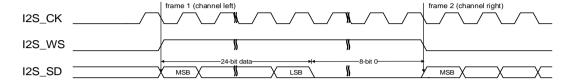

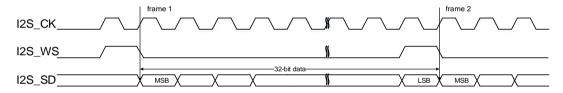

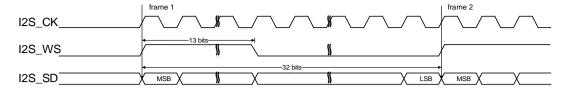

| Figure 18-14. I2S Phillips standard timing diagram (DTLEN=10, CHLEN=1, CKPL=0)              | 390          |

| Figure 18-15. I2S Phillips standard timing diagram (DTLEN=10, CHLEN=1, CKPL=1)              | 390          |

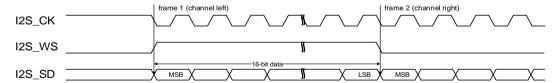

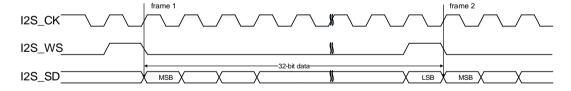

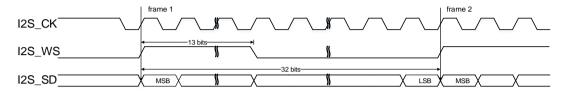

| Figure 18-16. I2S Phillips standard timing diagram (DTLEN=01, CHLEN=1, CKPL=0)              | 390          |

| Figure 18-17. I2S Phillips standard timing diagram (DTLEN=01, CHLEN=1, CKPL=1)              | 390          |

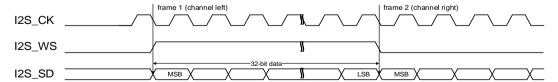

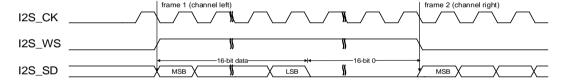

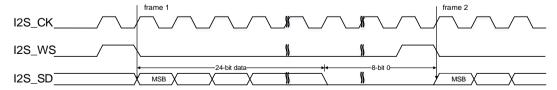

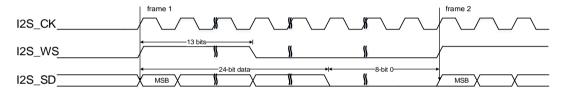

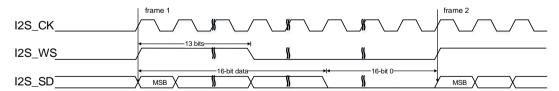

| Figure 18-18. I2S Phillips standard timing diagram (DTLEN=00, CHLEN=1, CKPL=0)              | 391          |

| Figure 18-19. I2S Phillips standard timing diagram (DTLEN=00, CHLEN=1, CKPL=1)              | 391          |

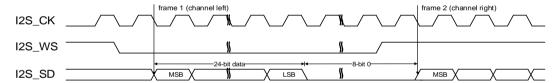

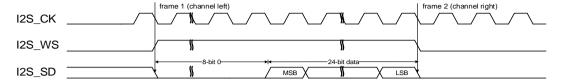

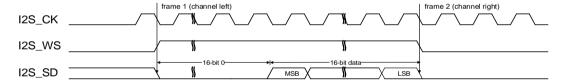

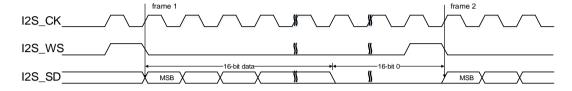

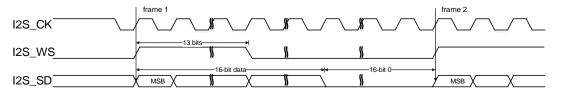

| Figure 18-20. MSB justified standard timing diagram (DTLEN=00, CHLEN=0, CKPL=0)             | 391          |

| Figure 18-21. MSB justified standard timing diagram (DTLEN=00, CHLEN=0, CKPL=1)             | 391          |

| Figure 18-22. MSB justified standard timing diagram (DTLEN=10, CHLEN=1, CKPL=0)             | 391          |

| Figure 18-23. MSB justified standard timing diagram (DTLEN=10, CHLEN=1, CKPL=1)             | 392          |

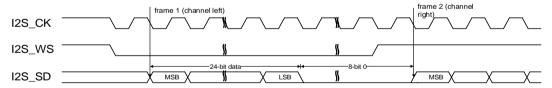

| Figure 18-24. MSB justified standard timing diagram (DTLEN=01, CHLEN=1, CKPL=0)             | 392          |

| Figure 18-25. MSB justified standard timing diagram (DTLEN=01, CHLEN=1, CKPL=1)             | 392          |

| Figure 18-26. MSB justified standard timing diagram (DTLEN=00, CHLEN=1, CKPL=0)             | 392          |

| Figure 18-27. MSB justified standard timing diagram (DTLEN=00, CHLEN=1, CKPL=1)             | 392          |

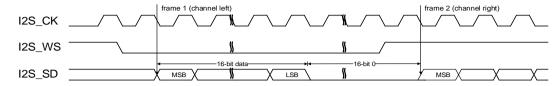

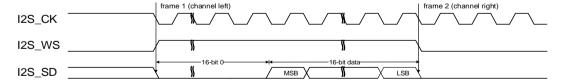

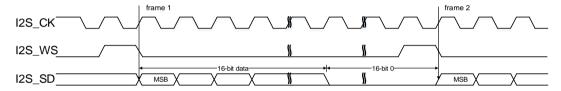

| Figure 18-28. LSB justified standard timing diagram (DTLEN=01, CHLEN=1, CKPL=0)             | 393          |

| Figure 18-29. LSB justified standard timing diagram (DTLEN=01, CHLEN=1, CKPL=1)             | 393          |

| Figure 18-30. LSB justified standard timing diagram (DTLEN=00, CHLEN=1, CKPL=0)             | 393          |

| Figure 18-31. LSB justified standard timing diagram (DTLEN=00, CHLEN=1, CKPL=1)             | 393          |

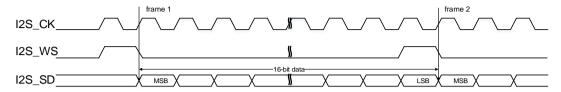

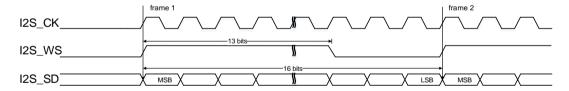

| Figure 18-32. PCM standard short frame synchronization mode timing diagram (DTLEN=00,       |              |

| CHLEN=0, CKPL=0)                                                                            | 394          |